# Man Machine Interface Design using Hardware Programming for Performance Enhancement

Dr. T. Harinath<sup>1</sup> and Dr. K. Lal Kishore<sup>2</sup> <sup>1</sup>Senior Manager, ECIL/Hyderabad, India Email: harnath.t@gmail.com <sup>2</sup>Professor, CVR College of Engineering/ECE Department, Hyderabad, India Email: lalkishorek@gmail.com

Abstract: Existing Embedded Systems are designed using a microprocessor. Design methodology of the embedded system depends on the architecture of the microprocessor used. Architecture of these embedded system designs have total dependence on the architecture of the microprocessor used. Study and analysis of various embedded system designs for the past thirty years revealed that there are several other design, development and manufacturing related issues with the microprocessor based designs like speed of processing, power consumption, excessive utilization of silicon, etc. Objective of this paper is to critically examine the design requirements for Man Machine Interface Logic, which is an embedded system and ascertain the issues in the existing designs. Hardware Programming, an innovative conceptual solution is proposed to overcome the issues observed by designing an embedded system without using any microprocessor. Design approach and design methodology based on Hardware Programming have been presented. Concepts of designing Man Machine Interface logic using Hardware Programming have been elaborated. Comparative Analysis is provided to ensure both the qualitative and quantitative improvement in performance. Performance is gauged in terms of both qualitative and quantitative parameters.

*Index Terms:* Embedded System, Protocol Analysis, Architecture, Silicon Utilization, Latency, Man Machine Interface, Hardware Programming

#### I. INTRODUCTION

#### A. Man Machine Interface

Man Machine Interface (MMI) logic is a subsystem used in an electronic system for incorporating control, status, system and storage operations. These operations facilitate user in selecting different sets of parameters among the available groups for carrying out different activities without any design changes, whether hardware or software [1], [2]. In other words, MMI logic is meant for incorporating programmability feature to an embedded system. MMI logic itself is an independent embedded system. Transfer of information to and from the system is through interfaces [3]. MMI has five types of interfaces. They are input interface, output interface, I/O interface, system interface and memory interface. Collection of control information is through input interface from input devices like keypad. Display of output status information is through output interface to output devices like Liquid Crystal Display (LCD), Light Emitting Diodes (LED). Bidirectional flow of information is through interfaces using I/O devices like Universal I/O Asynchronous Receiver Transmitter (UART). Non-volatile storage of control and configuration data is done nonvolatile memory like Serial Peripheral Interface (SPI) Flash memory using storage interface. Passing on the user fed control data and collection of system related status information is through system bus. UART is used for system bus. SPI is used for memory interface. Design methodology for MMI design is similar to any other embedded design. The factors to be concentrated on while designing MMI with a microprocessor are: Processing capabilities, Memory requirements, Data transfer mechanism, Integration with rest of the system and Clock requirements [4], [5].

Study and Analysis of various embedded systems design for the past 30 years have lead to the categorization of embedded systems design into following types:

- Embedded System using Hard Processor

- Embedded System using Soft Processor

- Embedded System using Multi-Core Hard Processor

- > Embedded System using Multiple Processors

- Embedded System using Micro Controller

- Embedded System using embedded hard processor on Field Programmable Gate Array (FPGA) and reconfigurable logic on the same FPGA

- Embedded System using Digital Signal Processor

- Combination of two or more of the above

The Trends being followed in latest embedded system design are:

- System Design with Multiple Processors and Multi Core Processors [6], [7], [8].

- System Design with Micro Controllers and Peripherals on same chip

- ➢ Hardware/ Software Co-Design

- Heterogeneous Embedded System Design

- > FPGA based Embedded System Design [9], [10], [11].

- ➤ Single Bit Processor based System [12].

- ▶ Distributed Co-operative Design Method [13], [14].

- ▶ Power Delay Reduction, Memory Efficient Techniques

- Dynamic Profiling [15].

#### B. Issues in Existing Embedded Systems

Several issues have been observed in embedded system design with respect to the design, performance, reliability and productivity in industrial application perspective. A list of the issues is given below.

- Architectural Dependence

- Multiple Skill Set Requirement

- Sequential Execution of Instructions

- Speed of Processing

- Large Memory Requirement

- Additional Resources Requirement

- Stringent Clock Requirement

- Excessive Utilization of Silicon

- High Power Consumption

- Design Complexity

- Huge Cost of Development

- Production / Manufacturing related issues

#### C. Possibilities of Replacing Microprocessor

Design of an embedded system revolves around the architecture of the microprocessor used. Main activities of an embedded system are classified into three parts, namely receiving the data input, processing the data and sending the output data. Data input is collected from different input sources. Received data received is processed by the preprogrammed algorithms and results are stored in memory. These processed outputs are sent out to output devices. For example, in case of a software defined radio, base band signal is received through a Coder Decoder (CODEC), various algorithms like modulation, filtering, etc are run on the base band signal received. Samples of modulated and filtered Intermediate Frequency (IF) are sent out to the Radio Frequency (RF) circuitry for further processing. In order to effectively implement the above three functions, a microprocessor is used.

The functions performed by the microprocessor used in an embedded system are: Accessing and controlling peripherals, scheduling events, processing of interrupts, managing memory, receiving data, executing algorithm, processing data and sending data. Microprocessor plays a supporting role in an embedded system and an embedded system can be designed with same specifications using different types of microprocessors / microcontrollers / digital signal processors. Hence, the focus of embedded system must be on receiving the inputs, computation of the algorithms and transmitting the processed data to the external world. If all the activities being executed by the microprocessor are implemented with some other logic or mechanisms, Microprocessor can be successfully replaced or avoided in the design of an embedded system.

## II. MMI DESIGN USING HARDWARE PROGRAMMING BASED DESIGN METHODOLOGY

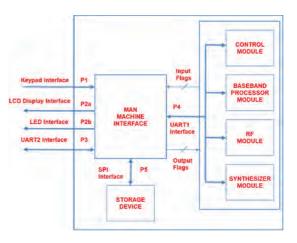

Hardware Programming based design methodology is an innovative technique to design an embedded system without using any microprocessor, but realizing the logic as well as driver applications using hardware programming with Hardware Description Language (HDL) like VHDL or Verilog HDL [16], [17], [18], [19]. This design methodology is applied for MMI logic that can be used in software defined radio project. This can be used in any other systems as well, for example, networking applications, nuclear applications and so on, with very minor changes. Figure1 illustrates the application of MMI in a system. As presented in the diagram, P1 is input interface. P2a and P2b are output interfaces, P3 is I/O interface. P4 is system interface and P5 is Memory interface.

Figure1. Application of Man Machine Interface

#### A. Identification of Activities

Activities of MMI Logic to be designed are:

- $\checkmark$  To ascertain the data entered through Keypad

- $\checkmark$  To provide appropriate messages on LCD Display

- ✓ To restrict the user access through passwords management

- ✓ To collect the user configuration data through asynchronous serial interface

- ✓ To authenticate the data access through asynchronous serial interface

- ✓ To provide replies to user through asynchronous serial interface

- ✓ To store user configuration data in non-volatile memory through synchronous serial interface

- ✓ To configure the system based on the user configuration data through asynchronous serial interface as system bus

- ✓ To collect the status information of entire system using system bus

- ✓ To provide user friendly menu driven operations

- ✓ To facilitate for erasure or modification of the configuration data based on the user commands

- ✓ To prepare preset channels for user convenience (A preset channel is a group of parameters and this entire group can be selected with a single key stroke)

## B. Dividing System into Functional Modules

In order to realize the functions identified above, logic of MMI module is divided into the following functional modules.

- a) Clock generation logic

- b) Keypad interface logic

- c) LCD display interface logic

- d) LED interface logic

- e) Key processing logic

- f) Serial peripheral interface logic

- g) UART1 receiver logic

- h) UART1 transmitter logic

- i) UART1 driver logic

- j) UART2 receiver logic

- k) UART2 transmitter logic

- 1) UART2 driver logic

- m) Passwords Management logic

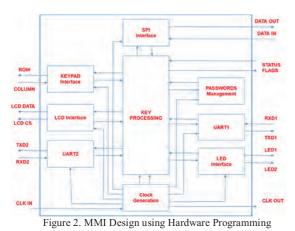

Modules (g), (h) and (i) are integrated to form UART1 logic. Modules (j), (k) and (l) are integrated to form UART2 logic. MMI logic design using hardware programming is shown in Figure 2. As shown in the figure, modules are categorized into peripheral modules, algorithm modules and clock & control modules. All the modules are independent in working and do not require microprocessor for its working. Keypad Interface Module, UART1 Receiver and UART2 receiver are input peripheral modules, LCD interface, LED interface, UART1 Transmitter and UART2 transmitter modules are output peripheral modules. UART1 Driver, UART2 Driver module and Passwords Management Module are algorithm modules. SPI interface module is an I/O peripheral module. Clock generation module and Key processing logic work together as clock and control module. Key processing logic performs control operations (i.e. generating required control signals) and also does the processing of the keypad interface output signals.

# C. Identifying the Events of Functional Modules

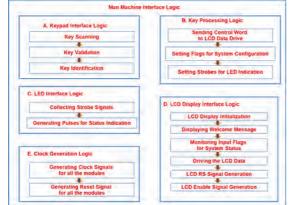

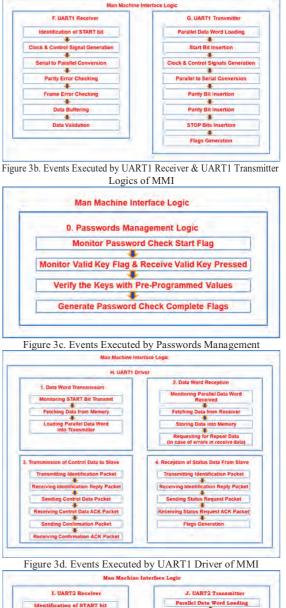

Figure 3a through Figure 3h depict the events executed by various modules of MMI logic.

Figure 3e. Events Executed by UART2 Receiver & UART2 Transmitter Logics of MMI

| 10.000                        |                                                                   |

|-------------------------------|-------------------------------------------------------------------|

| K. UAF                        | RT2 Driver                                                        |

| 1. Data Transmission          | 2. Data Reception                                                 |

| Manager Property and Tanadara | Monitoring Output Flags of Receive                                |

| Menitoring START Bit Transmit | •                                                                 |

| Fetching Data from Memory     | Fetching Data from Receiver                                       |

| +                             | Storing Data into Memory                                          |

| Loading Parallel Data Word    | +                                                                 |

| into Transmitter              | Requesting for Repeat Data<br>(in case of errors in receive data) |

Figure 3f. Events Executed by UART2 Driver Logic of MMI

Figure 3g. Events Executed by SPI Receiver and SPI Transmitter Logics of MMI

Figure 3h. Events Executed by SPI Driver Logic of MMI

## D. Analysis of Protocol

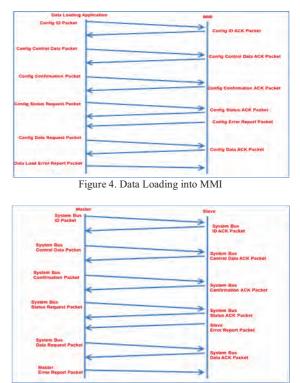

Protocol analysis is to be done for getting the particulars of sources & destinations of data, packet transfer information, and extraction & insertion of data in packet structures. MMI gets inputs from different sources. Key pressed information coming from keypad, Configuration data or algorithm related data from UART2, System related information from different slave devices through UART1, and Configuration data stored in non-volatile memory fetched through SPI interface are the various inputs to MMI logic. Processed data is given as output to multiple destinations. Messages related to control and status information are sent to LCD display. Status information is given to LEDs for continuous glowing or blinking of LEDs. Configuration data available in the system is given on demand through UART2. Reply messages to user queries are also given through UART2. Configuration data and control data are given to multiple slave devices of the system through system bus. Configuration data is loaded into non-volatile memory through SPI interface. Selective data is given to the appropriate modules inside the MMI logic for processing and computation of algorithms. Transfer of data from various sources to different destinations is done in many methods. Key press data is passed on in the form of logic levels on rows and columns. Different packet structures are used for Configuration UART and System bus UART. Configuration UART is for point to point communication. Figure4 shows the details of packets exchanged in the process of getting configuration data. System bus UART is used in point to multi point configuration. MMI is configured as the master and other system modules as slave devices. Master device only initiates communication. The details of packets exchanged for system bus communication to pass on control data / configuration data / algorithm related data / status information is shown in Figure 5. Non-volatile memory

access is through SPI interface, wherein MMI is master and Non-Volatile memory is slave. Different commands are sent by Master along with address to write data into memory, to read data from memory, to erase sectors and to bulk erase operations etc., Slave select is active, i.e., at logic level low till the communication between master and slave devices taking place.

Figure 5. Flow of Packets through System Bus

## E. Generation of Clock and Timing Signals

In order to ensure that all the events are executed at predictable time intervals, all the modules are designed to operate in synchronous mode. To avoid ambiguities, events are started or completed at known intervals of time. Single clock input is sufficient for MMI logic. All the other clock signals required for different modules are generated in clock generation module. A clock of 32.768 MHz clock is given as input. Some of the clocks required for internal operations of different modules are generated within those respective individual modules. Timing signals also are derived within those respective individual modules.

## F. Receiving Data

The input data streams points must be analyzed for type of data, its availability, format and destinations for the data transfer between modules within MMI. Keypad interface logic provides valid key press output, corresponding row data and validation flag. This information is made available to key processing logic. UART1 receiver provides valid data output (in data words) and valid data flag to UART1 Driver. UART2 receiver generates valid data words received and valid data flag for UART2 Driver module. Receiver of SPI module generates parallel data output along with corresponding flags for the master driver of SPI to take up further processing of data packets.

## G. Setting of Flags

Status of different operations is given in the form of setting Flags by individual modules. This will enable the concerned modules to initiate further activities. Key processing module performs control activities of MMI in addition to the processing of keys pressed to invoke certain events. Different operations selected through Keypad are: to allow data reception from UART2, to verify and authenticate the incoming data, to transfer algorithm related data from one segment to the other within the same nonvolatile memory, to set configuration data for a selected operation of the system, to erase the configuration data, to ascertain status, to print control and status messages on LCD display etc. Keypad entries are not accepted during the process of transactions with non-volatile memory. Configuration data from UART2 is communicated through the exchange of a series of packets. Different flags are set to indicate the successful extraction of required data and information about errors in the received data. These flags are used to enable storage of data or to transmit data through system bus. UART1 data is analysed to monitor the status of different slave devices on system bus. Respective flags are set or reset accordingly. These flags are used for status indication on LCD display or LEDs. SPI Flags related to the status of data transfer and data erase operations being carried out with non-volatile memory are used for the purpose of displaying appropriate messages on LCD and also for initiating certain activities by the system.

## H. Storage of Data

For performing data storage, points to be analysed are: data to be stored in Random Access Memory (RAM), data to be stored in Non-Volatile Random Access Memory (NVRAM), processing of NVRAM data, organization of RAM data and organization of NVRAM data. Configuration data, algorithm related data and preset channels data are stored in NVRAM. Initially with power ON or after reset operation, configuration and algorithm related data available in NVRAM is fetched and loaded into different segments of the RAM built with block RAMs of FPGA. Then flags are set accordingly to make system work as per the settings. Non-volatile memory is accessed through synchronous mode. Initially, configuration data is stored in RAM and after receiving the confirmation command from user, this data is dumped into NVRAM. Display messages are fixed and are stored as ASCII data in Read Only Memory designed with the look up tables of FPGA.

## I. Processing of Data

Incoming data packets are processed to get the actual data. In MMI logic – keys, configuration and algorithm related data, stored data and status information are processed by different algorithm modules. Outcome of these algorithms are: To authorize the user in choosing parameters for different operations (through two-level passwords), to extract data for use in the system, to select the message to be displayed on LCD, to set / reset flags related to the status of slave devices of the system and so on.

## J. Transferring the Processed Data

After processing the data, it should be made available at output peripheral modules and I/O peripheral modules. Data

transfer through UART2 is done by exchange of different packets. These data packets contain a few keywords in addition to the actual data. UART2 transmitter will transmit data in serial fashion according to the protocol. Flags indicating the status regarding start bit transmit, transmit process in progress are monitored to avoid data overwrite and also to ensure error free transmission. Control data packets are shared with different modules of the system through UART1. As master slave configuration is adopted, transfer of data to slave devices will be done one after the other in a sequence with proper care. Similarly, status is collected from slave modules in a sequence by giving commands sequentially. With power on or with reset, status is obtained from slave devices by giving appropriate control commands. Later, exchange of control and status data is done depending on user demands through keypad. Flags of UART1 transmitter are continuously monitored by UART1 driver for smooth transfer of data. Data loading into nonvolatile memory takes place through SPI interface depending on the user commands. Master driver of SPI interface logic arranges data as per the frame structure. Address and type of operations must be indicated clearly in their respective fields of the data frames. Slave select must be asserted low for the entire duration of data transfer.

## K. Enabling / Disabling the Logic

To reduce power consumption, selective enabling / disabling of the logic is done in the following ways.

- To restrict unwanted operations by providing control signals to the concerned logics

- To shut down unused logic at any instant by supplying control signals to the concerned logics.

- To gate the clocks to ensure that clocks are not supplied to unused modules at any point of time.

#### III. IMPLEMENTATION OF MMI LOGIC USING HARDWARE PROGRAMMING

XILINX Software ISE Design Suite 14.5 is used for various design activities of MMI like Design entry, Simulation, Implementation (Translate, Mapping and Place & Route), Programming File Generation, and Configuration of the Device. MMI logic is realized using SPARTAN 3AN XC3S1400AN device. The same MMI logic could be successfully ported on XC3S1600E device and different other devices of Virtex5 and Virtex6 families from XILINX and also on ALTERA devices like Cyclone II and Stratix Family FPGA devices. Device utilization summary of MMI logic is given in Figure 6. As shown in Figure 6, MMI logic consumed 1548 numbers of Slice Flip-Flops, 2520Nos of Occupied Slices and 4553Nos of 4-input LUTs and 16Nos of Block RAMs. Table-1 gives the summary of synthesis results of various modules used in MMI logic.

| Degra Danion     Sources     Sources  | 1915_Logic Project Status (11/25/2018063757)  |                          |               |                                |                       |             |                            |  |   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--------------------------|---------------|--------------------------------|-----------------------|-------------|----------------------------|--|---|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Project File: MC_Logic vise                   |                          | Parser Errors |                                |                       | Nei         | No Bhos                    |  |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Hodule Name:                                  | ME_Lopc                  |               | Implementation 5               | Implementation State: |             | Programming File Generated |  |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Target Device:                                | uclasi400an-Sfight/6     |               | +Errors:                       | + firmers:            |             | Ne Bros                    |  |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Product Version:                              | ISE 14.5                 |               | • Warnings:                    | • Warrings:           |             | 3 Namiros (2 nev.)         |  |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Design Goalt                                  | Balanted                 |               | +Routing Re                    | +kooting Results:     |             | Sprais Completely Routed   |  |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Design Strategy:                              | (Viro Default (unlocked) |               | <ul> <li>Timing Cor</li> </ul> | + Timing Constraints: |             | Constraints Het            |  |   |

| Synthesis Messages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Environment:                                  | System Settings          | -             | + Final Timin                  | g Score:              | 00          | Timing Report)             |  |   |

| Translation Messages<br>Map Messages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                               |                          |               |                                |                       |             |                            |  |   |

| Press self-bask Meages     Treise Meages     Series Meage     Series Meage     Series Meage     Market Meages     Series Meage     Market | Device Utikation Summary                      |                          |               |                                |                       |             |                            |  |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Logic Utilization                             |                          | Used          | Available                      |                       | Utilization | Note(s)                    |  | - |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Number of Sice Fig Rops                       |                          | 1             | -8                             | 22,528                | 4           | ñi l                       |  |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Number of Amplit UUTs                         |                          | . 6           | HB                             | 22,538                | 1           | ñ                          |  | _ |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Number of occupied Sices                      |                          | 2             | 120                            | 11,254                | 2           | 5                          |  | _ |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Number of Sices containing only related logic |                          | 2             | 20                             | 2,538                 | 1           | 6                          |  | _ |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Number of Sizes containing units              | leted logic              |               | ġ.                             | 2,520                 | 1           | 6                          |  |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Tatal Number of Finput LUTs                   |                          | ť             | 53                             | 22,538                | 1           | 15                         |  | _ |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Number used as kop:                           |                          | -4            | 179                            |                       |             |                            |  | - |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Number used as a multe-finu                   |                          | 3             | 10                             |                       |             |                            |  | _ |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Number used for Dual Port 3,0%                |                          | 1             | 4                              |                       |             |                            |  | _ |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Number of bonded 1085                         |                          |               | 60 500                         |                       | 1           | 15%                        |  |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 338 Rip Flaps                                 |                          | 1             | 13                             |                       |             |                            |  | - |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Number of BUFGHU'S                            |                          | 1             | 8                              | Ĵ¥                    | 3           | ñ                          |  |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Number of RAMELIEWES                          |                          |               | 15                             | ų                     | 9           | 6                          |  |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Average Perout of Nan-Clock Nets              | E.                       | 4             | 29                             |                       |             |                            |  |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                               |                          |               |                                |                       |             |                            |  |   |