# FPGA Implementation of MC-CDMA for High Security Applications

R.Ganesh<sup>1</sup> and Ch.Sandeep Reddy<sup>2</sup> <sup>1</sup>CVR College of Engineering/ECE Department, Hyderabad, India Email: rachaganesh@gmail.com <sup>2</sup>CVR College of Engineering/ECE Departments, Hyderabad, India Email: sandeepredy.ch@gmail.com

Abstract-The demand of wireless communications is increased in high speed, high security applications like missile communication, satellite communication etc. The communication with these features can be achieved by using different carrier modulation techniques like single carrier, multi carrier modulation etc. The multi carrier modulation with orthogonality of carriers provides high speed communication. This process is called Orthogonal Frequency Division Multiplexing (OFDM). The high speed and band width utilization can be achieved by using OFDM. The high security communication can be achieved by using coders and spreaders with different random generator sequences with the help of Spread Spectrum techniques. This can be done by using a method called Code Division Multiple Access (CDMA). The Multi Carrier CDMA is defined by adding the features of OFDM and CDMA and this is used for high speed and high secured communication system. The MC-CDMA uses convolution coder, viterbi decoder and spreader, de spreader etc to provide security.

The MC-CDMA technique consists of a back to back connected transmitter and receiver with 8-point FFT/IFFT and QPSK modulation. This technique is designed by using Verilog HDL with Xilinx ISE Design suite 12.4 version tool. The design is implemented in Xilinx virtex-5 XUPV5LX110T FPGA board.

*Index Terms*—OFDM, CDMA, Orthogonality, Convolution Encoder, Viterbi Decoder.

# I. INTRODUCTION

The present communication systems components require high speed and high security in different application areas like missiles, satellites, mobile etc. The high speed or high security communication systems alone may creates some problems related to bandwidth inefficiency, spectrum utilization etc [1].To achieve better non functional performance parameters the high speed features of OFDM and security features of CDMA are combined to get a new technique called as Multi Carrier CDMA (MC-CDMA).

The MC-CDMA is one of the spectrum utilization techniques that are used for multiple access schemes. This technique gives best spectrum utilization, flexibility in terms of speed and security.

This paper explains the FPGA implementation of MC-CDMA for high security applications. This paper is organized such that the section 2 describes the introduction of basic wireless communication models for high speed, high security applications by using multi carrier techniques like OFDM, CDMA, and MC-CDMA, section 3 describes the results of MC-CDMA system by using Xilinx ISE tools, and section 4 describes the FPGA implementation of MC-CDMA by using Xilinx virtex5 FPGA. The conclusion is presented in section 5 followed by references.

# II. OVERVIEW OF MC-CDMA

In wireless communication the data can be sent through the channel in two ways i.e. either singlecarrier or multi-carrier. In single-carrier technique the available data stream is transferred sequentially, in this technique each modulated carrier occupies the entire bandwidth of the channel. But, in the multi-carrier technique the total bandwidth is divided into different sub frequencies so that each frequency can be used for one data input. This division of frequency gives better bandwidth spectrum utilization.

The single data input system uses one carrier signal with the total bandwidth allotted to this channel only. In multiple data input system the bandwidth is divided into N number of carrier signals for N inputs. The bandwidth utilization for single input and multiple input systems is shown in Figure 1.

Figure.1: Difference between single-carrier and multi-carrier

Based on the application the multi-carrier technique is divided in to different types like CDMA (Code Division Multiple Access), OFDM (Orthogonal Frequency Division Multiplexing) and

MC-CDMA (Multi-Carrier Code Division Multiple Access) etc. The CDMA can be implemented by using the spreading techniques, so it is used for high security applications. In OFDM the available spectrum is divided into N number of orthogonal sub carriers and this technique is used for high speed applications. The MC-CDMA technique is designed by adding the high speed features of OFDM and security features of CDMA [7]. The MC-CDMA uses frequency domain to spread the data, in this technique each sub carrier is having different spreading code. Another spreading technique called as MC-DS-CDMA spreads data in time domain, in this technique all sub carriers uses common spreading code. This concept of multiple spreading codes and single spreading codes for multi carrier design is shown in Figure2 (Fig2.a and Fig. 2.b).

Figure. 2(a) MC-CDMA

Figure. 2(b) MC-DS-CDMA

Figure 2: Classification of MC-CDMA

Advantages of MC-CDMA:

- 1. Higher data rates with better bandwidth utilization.

- 2. Best suitable for wireless systems with delay spread, Doppler spread.

- 3. Fading is reduced by using frequency diversity.

- 4. Limited energy loss due to the scattering of energy in all sub carriers.

Problems in MC-CDMA:

1. Peak-to-Mean Envelope Power Ratio (PMEPR) is high due to non linearity in amplification.

2. For high speed vehicles designs complex analysis is required because of carrier frequency offset sensitivity.

3. Sensitive to phase noise.

4. The frequency reusing factor is less compared to other techniques.

## Block diagram of MC-CDMA:

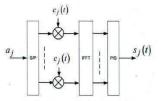

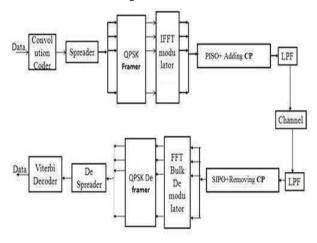

The MC-CDMA communication system at base band level can be designed by using a transmitter and a receiver section. This design of transmitter and receiver consists of both security features using multi carriers with the help of encoders, decoders and speed features using OFDM with QPSK modulation/demodulation techniques. The transmitter section consists of convolution encoder, QPSK framer, IFFT etc. The receiver section consists of FFT, QPSK deframer, viterbi encoder etc. The block diagram of the MC-CDMA is shown in Figure3.

Figure 3: Block diagram of MC-CDMA

The individual blocks of MC-CDMA are explained below with respect to functionality.

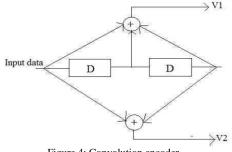

### Convolution Encoder:

The convolution encoder is used for security purpose, it will convert single bit input to two bit or multi bit output [12]. Convolution encoder is represented by (n, k, m) notation, where n is the number of output bits, k is the number of input bits and m is the constrained length. The rate of convolution encoder is defined as the ratio of number of input bits to number of output bits. It can be implemented by using FSM (Finite State Machine). The Figure 4 below illustrates a simple convolutional coder with k=1, n=2, g1 (n) = (1 0 1), g2 (n) = (1 1 1) and R=1/2. Where R is the code rate.

Figure 4: Convolution encoder

The state table for convolution encoder is shown in Table1indicating input, present state, next state and output values.

TABLE I STATE TABLE OF CONVOLUTION ENCODER

| Input | Present state | Next state | Output  |  |  |

|-------|---------------|------------|---------|--|--|

| ( u ) | (S1,S0)       | (S1,S0)    | (V1,V2) |  |  |

| 0     | 00            | 00         | 00      |  |  |

| 1     | 00            | 10         | 11      |  |  |

| 0     | 01            | 00         | 11      |  |  |

| 1     | 01            | 10         | 00      |  |  |

| 0     | 10            | 01         | 10      |  |  |

| 1     | 10            | 11         | 01      |  |  |

| 0     | 11            | 01         | 01      |  |  |

| 1     | 11            | 11         | 10      |  |  |

The state diagram and the trellis diagram of  $\frac{1}{2}$  convolution encoder in Figure 4 are shown below Figure 5.a and 5.b.

Spreader:

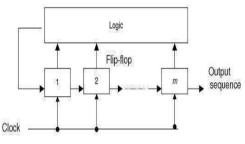

The Spreader is also used for security purpose. This can be implemented by using Linear Feedback Shift Register (LFSR). The m-stage LFSR block diagram is shown in Figure 6.

Figure 6: m-stage LFSR block diagram

The LFSR can be designed by using flip flops and some combinational logic circuit. The values in the flip flops are shifted by a single timing clock. The logic in the above diagram can be implemented by using the EXOR gates. The output of EXOR gate is feedback to the input of the LFSR.

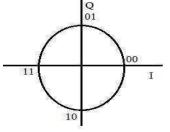

## QPSK Framer:

The Quadrature Phase Shift Keying (QPSK) is used to modulate the input data signal with the carrier by using four combinations of real and imaginary I and

CVR College of Engineering

Q channels [8]. The selection of I and Q channels can be done by using the one of four possible carrier phase shifts (0,  $\Pi/2$ ,  $\Pi$ , and  $3\Pi/2$ ). This mapping of I and Q channels to the input two bits in the form of constellation diagram is shown in Figure 7.

Figure7: QPSK Constellation diagram

#### IFFT (Inverse FFT) Modulator:

The IFFT is used in the transmitter section of MC-CDMA to minimize the complexity of the design. The IFFT is an algorithm that is useful for speeding up the computation and converts frequency domain to time domain [5].

The DFT of a sequence  $\{x(n)\}$  of length N by a complex valued sequence  $\{X(K)\}$

$$X(K) = \sum\nolimits_{n=0}^{N-1} x(n) e^{n} \left(-\frac{j \text{zpink}}{N}\right) \quad , \ 0 \leq k \leq N\text{-}1.$$

Let  $W_N$  be the complex-valued phase factor, which is an N th root of unity expressed by

$W_N = e^{-j2\pi/N}$

Hence X(K) becomes

$$X(K) = \sum_{n=0}^{N-1} x(n) W_N^{nk}$$

,  $0 \le k \le N-1$ .

Similarly Inverse Discrete Fourier Transform (IDFT) become

$$K(n) = 1/N \sum_{k=0}^{N-1} X(k) W_N^{-nk}$$

,  $0 \le n \le N-1$ .

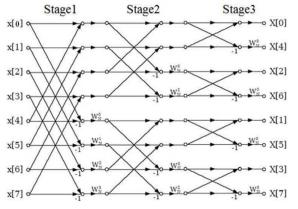

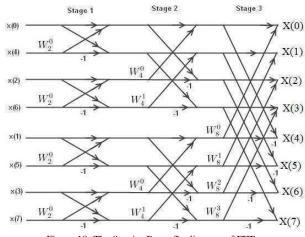

The butterfly diagram of 8-point IFFT is shown in Figure 8.

Figure 8: Butterfly diagram of 8-point IFFT

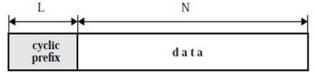

## PISO (Parallel In Serial Out):

The parallel in serial out block accepts parallel data and produces serial data as output. The Inter Symbol Interference (ISI) problem of OFDM can be minimized by adding a guard time is inserted with duration longer than the multipath channel maximum delay. This ISI effect can be removed by extending this guard time cyclically in OFDM symbol. The cyclically extension of an OFDM symbol is shown in Figure 9.

Figure 9: PISO with addition of CP

#### SIPO (Serial In Parallel Out):

The serial data can be converted into parallel data by using this block. Before applying the outputs of SIPO to FFT (Fast Fourier Transform) demodulator cyclic prefix can be removed.

#### FFT (Fast Fourier Transform) demodulator:

To reduce the complexity of MC-CDMA, Fast Fourier Transform (FFT) technique is used in receiver [6]. The FFT is used to convert from time domain to frequency domain.

The FFT is an algorithm that is useful for speeding up the computation. The 8-point FFT butterfly diagram is shown in Figure 10.

Figure 10: The 8-point Butterfly diagram of FFT

#### QPSK Deframer:

The parallel data bits are taken two bits together and converted from I, Q to the data bit pattern. The parallel data is converted into serial data. This operation is exactly reverse to QPSK framer.

Despreader:

The serial data is again Exclusive-ORed with the PN pattern and resulting in original data bit pattern. *Viterbi Decoder:*

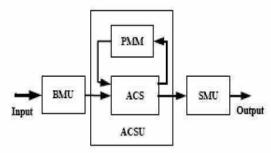

The viterbi decoder is used to decode the output of the convolution encoder [11]. Block diagram of the viterbi decoder is shown in Figure 11.

Figure 11: Block diagram of the viterbi decoder

The Viterbi decoder is designed by using Branch Metric Unit (BMU), Add Compare Select Unit (ACSU), and State Metric Unit (SMU) [13-15]. The branch metric computation block is used to count the number of differing bits in the received code symbol and expected code symbol. This is called as hamming distance. The ACSU makes a sum of branch metric and previously accumulated path metric, compare the path metric and select the smallest path metric and decision bits that are supplied to SMU. The SMU finds out the survivor path and decoding bits, SMU produces the decoded bits.

#### III. RESULTS OF MC-CDMA

The design of MC-CDMA is implemented on Xilinx ISE (Integrated Software Environment) tools; the design is simulated by using Isim simulator and synthesized by using XST (Xilinx Synthesis Tool).The design is prototyped on to XUPV5LX110T FGPA board using IMPACT configuration tool.

The simulation results of MC-CDMA transmitter and receiver are shown below figures 12 and 13.

| Name                | Yalue                                   | 0.06     | 100ns                                   | 200 ns     | 900 ns          | 400 ns   | 900 ns         | 600 ns                  | 700 rs                                        | 800ns                                                                                                          | 900 ns         |

|---------------------|-----------------------------------------|----------|-----------------------------------------|------------|-----------------|----------|----------------|-------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------|

| l <mark>e</mark> dk | 1                                       | 10000    |                                         |            |                 |          |                | UUUUU                   |                                               |                                                                                                                |                |

| la rst              | 1                                       |          |                                         |            |                 |          |                |                         |                                               |                                                                                                                |                |

| h (20)              | 0000                                    | ~        |                                         | 0001       |                 | γ        |                | 0010                    |                                               | γ                                                                                                              | 0011           |

| M temp[30]          | 0000                                    |          | η                                       | 000        |                 |          |                | 000                     | -                                             | X.X.X.                                                                                                         | 1000           |

| <b>N</b> (40]       | 0                                       |          |                                         |            | NS/GITTING      |          | SVEV7Y8Y       | 9 (10) 11) 12) (13) (14 | NG GRAD AND AND AND AND AND AND AND AND AND A | the second s | a free freeman |

| N qout[7:0]         | 0000000                                 | 00000    | 100000000000000000000000000000000000000 |            | 000011          |          | Y              |                         | 0001110                                       |                                                                                                                | XO             |

| 🚺 temp[15:0]        | 000000000000000000000000000000000000000 |          |                                         |            | nnnr            |          | (100000). Y    | 0000                    | mm                                            | $\overline{n}$                                                                                                 | 20010000000.   |

| M (40)              | 8                                       |          | 5)6)7)8)9                               |            | (15)(6)(7)(8)(9 |          |                |                         | 1516(7)(8)(9                                  | කත කත ශ                                                                                                        | 1 20 2 20      |

|                     | 000000000000000000                      |          | 00000                                   |            |                 |          | Y              | and and and and and an  | 00000000000                                   |                                                                                                                | )(010000       |

|                     | 000000000000000000000000000000000000000 |          |                                         |            | 0               |          | τ <del>ί</del> | 1100                    | 000000000000000000000000000000000000000       |                                                                                                                | )(00100000     |

| <b>1</b> x0(1:0)    | 00                                      |          |                                         | 0          |                 |          | X              |                         | 10                                            |                                                                                                                | X 11           |

| N st[150]           | 00                                      |          |                                         |            |                 | 0        |                |                         |                                               |                                                                                                                | Y 10           |

| N 12(110)           | 00                                      |          |                                         |            |                 | 0        |                |                         |                                               |                                                                                                                |                |

| N 13(1:0)           | 00                                      |          |                                         |            |                 | 0        |                |                         |                                               |                                                                                                                |                |

| N DR0(31:0)         | 3480000                                 |          |                                         | 390000     |                 | -        | χ              | -0                      | £f800000                                      |                                                                                                                | Yaao           |

| W DR1[31:0]         | 3£800000                                |          |                                         |            |                 | 3f800000 | -              |                         |                                               |                                                                                                                | )(5/800        |

| NO(31.0)            | 0000000                                 |          |                                         |            |                 | 000000   | -              | -                       |                                               |                                                                                                                | (6/800         |

| N DOD[31:0]         | 0000000                                 |          |                                         |            |                 | 000      | 000            |                         |                                               |                                                                                                                |                |

| ad(31:0)            | 3490000                                 |          |                                         | 330000     |                 |          | χ              | 1                       | 3720000                                       |                                                                                                                | )3x10          |

| <b>N</b> at(31:0)   | 00000000                                |          |                                         | ((((()))   |                 |          | χ              |                         | bedaileía                                     |                                                                                                                | )(bese         |

| <b>1</b> ara[31:0]  | 0000000                                 |          |                                         | 000000     |                 |          | χ              |                         | be:0000                                       |                                                                                                                | (3e00          |

| <b>H</b> 30(31.0)   | 0000000                                 |          | _                                       | (00000)    |                 |          | χ              |                         | 600000                                        |                                                                                                                | Xtelli         |

| 📲 at(31:0)          | 0000000                                 | <u> </u> |                                         | (((((((    |                 |          | X              |                         | 000000                                        |                                                                                                                | (bd3)          |

| <b>N</b> (31.0)     | 0000000                                 |          |                                         | (((((()))) |                 |          | X              |                         | 300000                                        |                                                                                                                | )ett           |

| • 📢 y[4:0]          | 0                                       |          | 56789                                   | 0000394    | (5)(6)(7)(8)(9  | 01237    | 5803           | 9000000                 | 56789                                         | <u>@@@@@</u> @                                                                                                 | 3800           |

| M temp[639:0]       | 8                                       | 200000   | 00000                                   | 00000      | 00000           | ( )      | )(3)           | 2000000                 | 00000                                         | 00000                                                                                                          | 10000          |

| <b>N</b> yr[31:0]   | 86388383                                |          | 7901-0 20980                            | 6666       |                 | 00000    | n              | h                       | mm                                            | (bel VYY                                                                                                       | hm             |

Figure 12: Simulation results of MC-CDMA transmitter

Figure 13: Simulation results of MC-CDMA receiver

CVR College of Engineering

## V. FPGA IMPLEMENTATION OF MC-CDMA

The design of MC-CDMA system is verified on Xilinx Virtex-5 FPGA by using Xilinx iMPACT tool. The output of MC-CDMA on virtex-5 FPGA is shown in Figure 14.

Figure 14: Output of MC-CDMA on Virtex-5 FPGA

## V. CONCLUSION

The design of MC-CDMA system is implemented with 8-point IFFT/FFT, QPSK modulation, spreader, de spreader, convolution encoder and viterbi decoder is designed by using Xilinx ISE Design suite 12.4 version with Verilog HDL.

The design is simulated for functionality by using Xilinx ISE simulator tool. The synthesized MC-CDMA design has 1382 LUT slices, 2005 slice registers and 3 buffers. Timing analysis results show that the critical path is 2.329 ns, i.e. the maximum clock frequency is 429.369 MHz

The synthesized MC-CDMA design is implemented on XILINX Virtex-5 FPGA.

#### REFERENCES

- Atul Govindrao Pawar, Wireless Communication in Missiles Challenges, DRDO Science Spectrum, March 2009, pp. 230-235. Per Hjalmar Lehne, Frode Bøhagen, OFDM for Wireless Communications, R & I Research Report R / 7 2008.

- [2] Zhiwei Tang\_ and Dongqin Sheng, Implementation of OFDM Based on FPGA, 2012 International Conference on Image, Vision and Computing, IPCSIT vol. 50(2012).

- [3] M.A. Mohamed, A.S. Samarah, and M.I. Fath Allah, Implementation of Adaptive OFDM System Using FPGA, IJCSI International Journal of Computer Science Issues, Vol. 9, Issue 3, No 3, May 2012.

- [4] Somayeh Mohammady, Nasri Sulaiman, Roslina M. Sidek, Pooria Varahram and M. Nizar Hamidon, FPGA Implementation of Inverse Fast Fourier Transform in Orthogonal Frequency Division Multiplexing Systems, Universiti Putra Malaysia (UPM)Malaysia.

- [5] K. Harikrishna, T. Rama Rao, and Vladimir A. Labay, FPGA Implementation of FFT Algorithm for OFDM Based IEEE 802.16d (Fixed WiMAX) Communications, Journal of Electronic Science and Technology, vol. 8, No. 3, September 2010

- [6] Ahmad R. S. Bahai ,Burton R. Saltzberg and Mustafa Ergen, tutorial on MultiCarrier Digital Communications Theory and Applications of OFDM.

- [7] Ron Hranac, report on QPSK and 16-QAM Digital Modulation by Cisco Systems.

- [8] K. Fazel and S. Faiser, Multi-Carrier and Spread Spectrum Systems from OFDM and MC-CDMA to LTE and Wi-MAX, Wiley publications 2008 edition.

- [9] Ayse Kourton, report on Spreading Codes in CDMA Detection, by Eastern Mediterranean University.

- [10] Anubhuti Khare, Manish Saxena and Jagdish Patel, FPGA Based Efficient Implementation of Viterbi Decoder, International Journal of Engineering and Advanced Technology (IJEAT), Volume-1, Issue-1, October 2011.

- [11]. Yan Sun and Zhizhong Ding, FPGA Design and Implementation of a Convolutional Encoder and a Viterbi Decoder Based on 802.11a for OFDM, Wireless Engineering and Technology, 2012, 3, 125-131.

- [12]. Pushpinder Kaur, report on Implementation Of Low Power Viterbi Decoder On FPGA, June 2006.

- [13]. Samirkumar Ranpara, report on On a Viterbi decoder design for low power Dissipation, Blacksburg, Virginia on April 1999.

- [14]. Hugo Santos, Mario Vestias, Horacio Neto and Helena Sarmento, Tradeoffs in the Design of a Viterbi Decoder for a MB-OFDM Receiver, PTDC/EEAELC/67993/2006.

- [15]. Minh Quang Nguyun, report on Design and Implementation of a Downlink MC-CDMA Receiver, Del University 2011.