# CVR JOURNAL OF SCIENCE & TECHNOLOGY

## **CVR COLLEGE OF ENGINEERING**

(An Autonomous College affiliated to JNTU Hyderabad)

Mangalpalli (V), Ibrahimpatnam (M),

R.R. District, Telangana. – 501510

http://cvr.ac.in

#### **EDITORIAL**

We are happy to bring out Volume 7 of the Biannual Journal of our college, CVR Journal of Science & Technology, with a wide spectrum of papers from different branches of Engineering, Science and Management. As was the case for the previous volumes, we received a number of papers. Out of the papers received, a limited number of 20 papers were selected for inclusion in the current volume, based on the recommendations made by the members of the Editorial Committee.

The breakup of the papers among the various disciplines is as follows:

The authors include staff members of our college and some from external institutions as coauthors. Three papers in Computer Science are from outside. The Computer Science papers span the important areas of Networking, Semantic Web and Component-based frameworks.

Topics selected for publication also include research work into advanced subjects like cognitive radio, software defined radio, image processing, chip design, data mining etc.

The papers that are selected from EEE cover advanced topics such as multilevel inverters and smart grid. Steps are already initiated by the government of India to transform conventional grids in to smart grid. The paper covers various aspects of smart meters which include technologies used in smart meters.

We hope that the interest of staff members of all the departments of our college will grow further in contributing their research work in the journal. We have been including some papers from external organizations and it will be our attempt to attract more numbers from outside so as to broaden the scope of our journal.

I am grateful to all the members of the Editorial Board for their help in short listing papers for inclusion in the current volume of the journal. I wish to thank Sri K. Venkateswara Rao, Associate Professor and Sri B. P. Deepak Kumar, Programmer in the Department of CSE for help in the preparation of the papers in camera ready form for final printing.

K.V.Chalapati Rao Editor

| Component based Frameworks for exporting Graphic functionality through automation layer <i>Dr. Hari Ramakrishna</i>                                                                                 | 1   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Using Domain Ontology and Sequential Rule Mining for Extracting Behavior Patterns from Web Navigation Logs C. Ramesh, Dr. K. V. Chalapati Rao and Dr. A. Govardhan                                  | 8   |

| Improving Performance of 802.11n Networks Using Various Rate Adaption Algorithms D. Arjun Mitra Reddy, B. Prathyusha and D. Amarendranath Reddy                                                     | 13  |

| Influence of Router Buffer Size on TCP Execution D. Arjun Mitra Reddy                                                                                                                               | 23  |

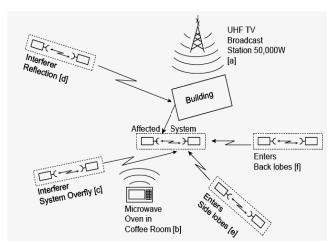

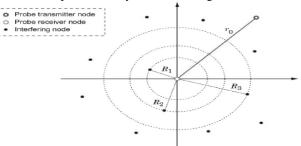

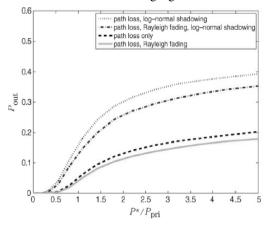

| Mathematical Analysis of Interference Issues and Study on Pathloss, Fading and Shadowing Effects on Cognitive Radio Networks <i>Ch. HemaLatha</i>                                                   | 33  |

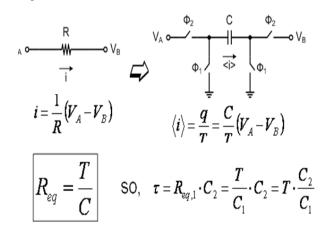

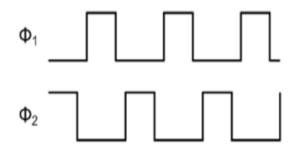

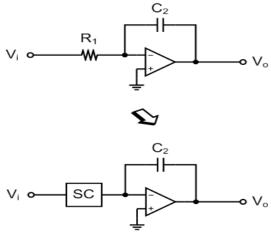

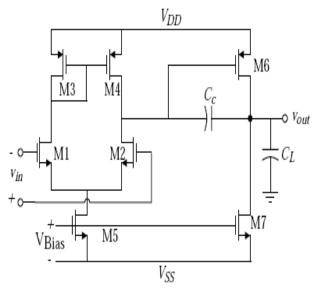

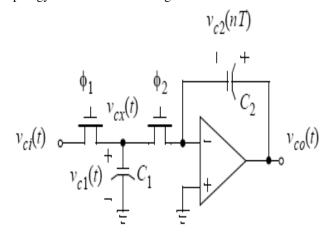

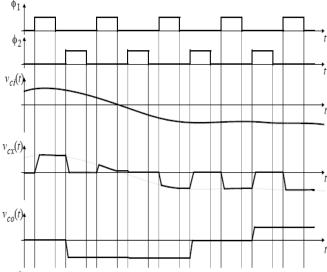

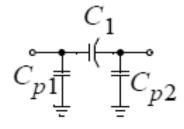

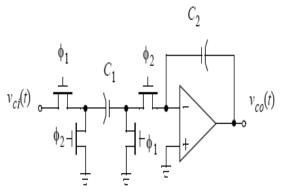

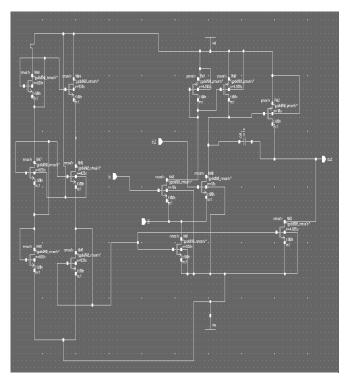

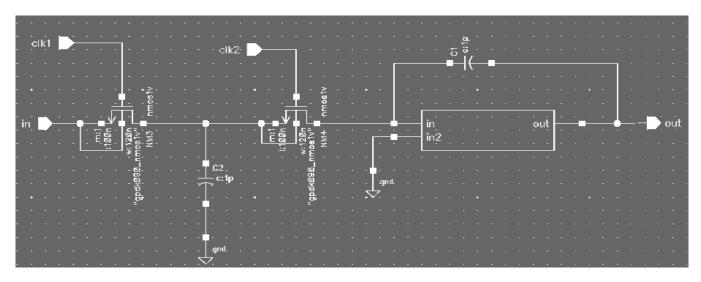

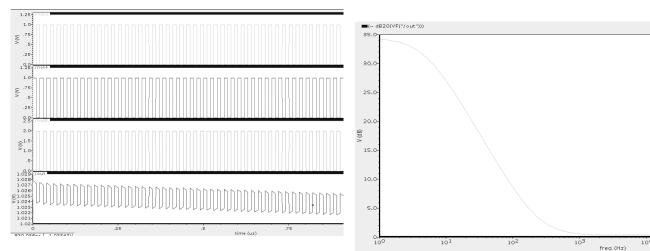

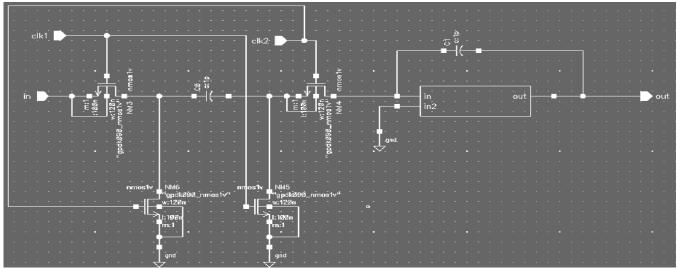

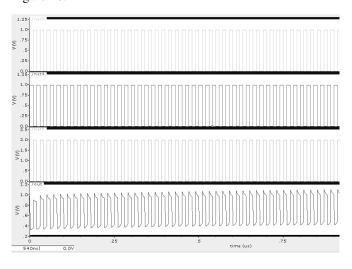

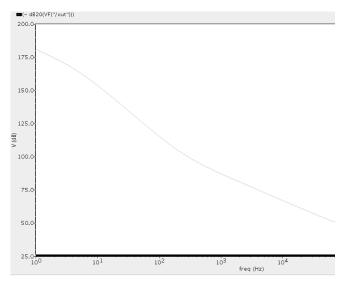

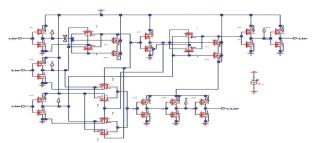

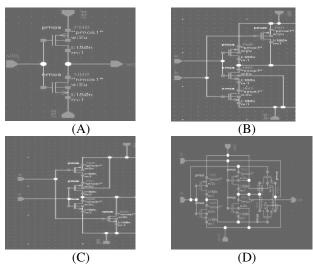

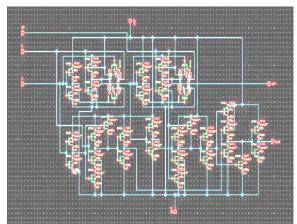

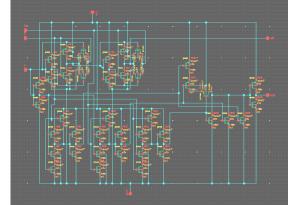

| Design of Switched Capacitor Integrators using 90nm Technology <i>R. Ganesh</i>                                                                                                                     | 37  |

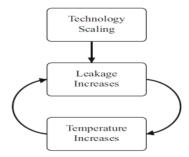

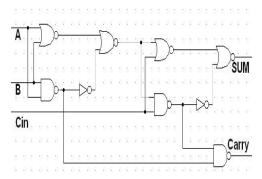

| Hazards and Glitch Power Reduction of CMOS Full Adder in 90nm Technology B. J. Singh                                                                                                                | 42  |

| Evaluation of Image Inpainting Algorithms  B. Janardhana Rao and O.Venkata Krishna                                                                                                                  | 48  |

| An efficient sense amplifier design for STT-RAM in 45nm hybrid CMOS process <i>Karrar Hussain</i>                                                                                                   | 53  |

| Reduction of ISI using RRC filter for Convolution codes with Viterbi Decoding R. Prakash Kumar and P. Naga Malleswari                                                                               | 57  |

| Implementation of BIST Technique for A to D Converters in FPGAs M.V. Sushumna                                                                                                                       | 62  |

| Comparative Analysis of Various Enhancement Methods for Satellite Images M. Vinod Kumar Reddy                                                                                                       | 69  |

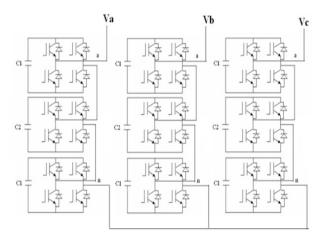

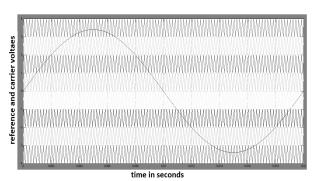

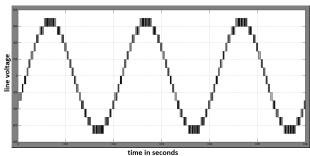

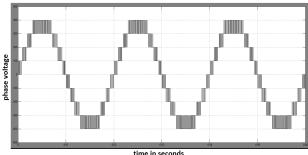

| Design of Multilevel Multicarrier H-Bridge Inverter fed Induction Motor Drive <i>P Vinod Kumar</i>                                                                                                  | 73  |

| Smart Meters in Future Power Grid: A Review M. Rajasree                                                                                                                                             | 77  |

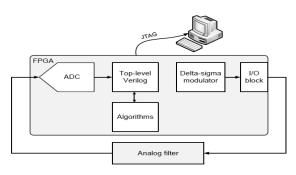

| The Test Bench for FPGA-based QPSK and QAM Modulators in Software defined radio O. Venkata Krishna and B. Janardhana Rao                                                                            | 83  |

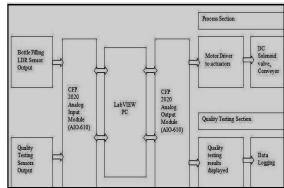

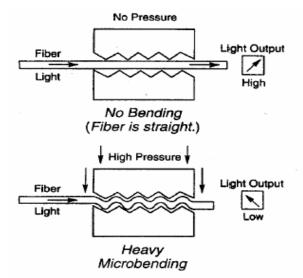

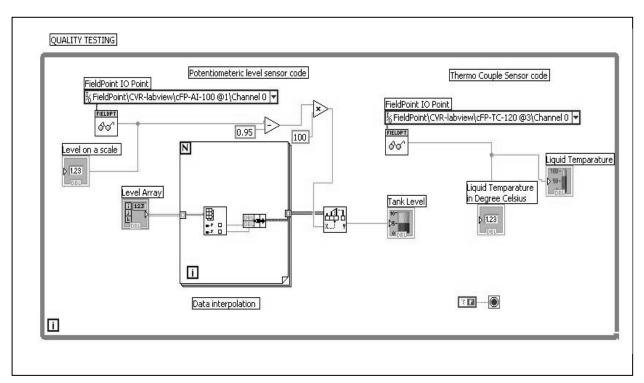

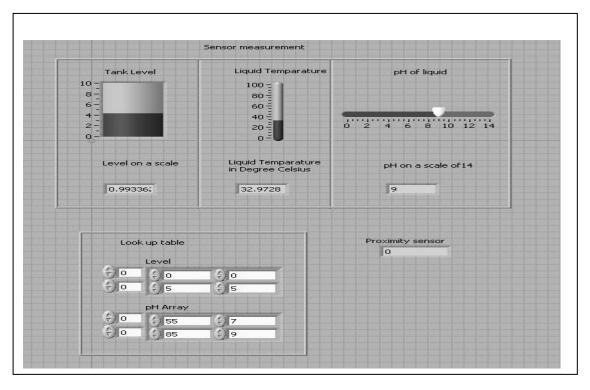

| Auto Quality Testing and Filling Station by using NI LabVIEW and Specially Designed OFS G. Venkateswarlu                                                                                            | 90  |

| Performance Assessment and Classification of Students using CAMP Model with Data Mining Approach Nayani Sateesh                                                                                     | 97  |

| Fourier Transform Infrared Spectroscopic Analysis of Medicinal Plant (Bhringaraj) from the Duvva Village West Godavari District, Andhra Pradesh, India <i>P. Saritha, N. Gandhi and D. Shirisha</i> | 101 |

| MHD Rivlin-Ericksen Free Convective Memory Flow through Porous Medium <i>Rafiuddin</i>                                                                                                              | 105 |

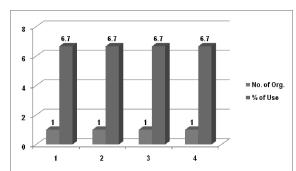

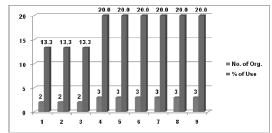

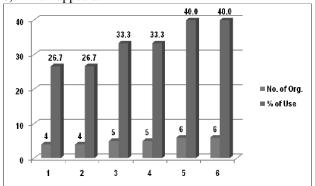

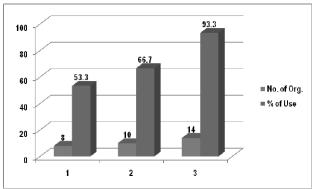

| Social Marketing Strategies Used For Fund Raising by NGOs Working in the Field of Disability Rehabilitation  Mr. Narendra Kumar and Dr. M.S.Bhat                                                    | 109 |

# Component based Frameworks for exporting Graphic functionality through automation layer

Dr. Hari Ramakrishna,

Department of Computer Science and Engineering, C.B.I.T, Hyderabad, India

Email: dr.hariramakrishna@rediffmail.com

Abstract— The Component technology though complex to implement has several advanced features in development of graphic frameworks. Pattern Frames are evolved to solve such complexities. This paper uses Microsoft COM Technology for providing solution. These principles enable common developer to use advanced technology for providing solutions using complex technology in a simple way and providing patterns to common client to use these in simple processes. It presents procedure of building automation process. As Microsoft changes procedures reorienting structures, these processes work in all versions though they are demonstrated in Visual Studio 6.0. Results obtained and code segments are also presented. Abstract pattern frame, Wrapper and other pattern frames and Helper object are presented.

Index Terms— Pattern- Frames, Automation Layer, IDL ODL script, Helper Object, Wrapper, Display files, Semantic graphic behavior, graphic components, graphic frameworks, debug driver tool, Microsoft graphic applications, object oriented models and frameworks. Dynamic display files. Component Object Model COM, Macros, Wizards.

#### I. INTRODUCTION

The software Industry is adopting new procedures and technologies for rapid development of software. The requirements of the industry and client are also changing rapidly. Though industry started with business and information processing applications, mainly for railways and other industries, now the industry's concentration is on total simulation of real time environment, knowledge extraction, decision making, rapid application development using frameworks, making developer independent of development environments, using reuse techniques and patterns and frameworks.

In this connection several frameworks are developed in computer graphics, computer based design CAD, Geographical Information system GIS, Industrial Plant designed system and several military systems [8,9,10,11]. The Intergraph Solid Edge, Imaginer, Smart Plant, Geological systems (GeoMedia) and several graphic frameworks have been developed in Microsoft Technology. They are exhibiting advanced technical features using Microsoft Technologies, namely COM Technology starting from Visual studio 2.0 from 1994 onwards.

COM technology has many advantages compared with Object Oriented Technology. But its implementation is very complex. Companies like Microsoft have provided several Wizards and frameworks stating from Visual Studio Versions 2.0, 4.0, 5.0, 6.0 and 7.0, and

subsequently .NET versions incorporating more and more technical features. The COM Framework of Microsoft implements almost all Design Patterns.

# II. OBJECT ORIENTED TECHNOLOGY VERSUS COMPONENT TECHNOLOGY

There are several unsolved problems in the present Object Oriented Technologies. A simple Object Oriented Technology cannot provide solutions to such problems. Typical problems one faces with the present object oriented technology are discussed below. [1-7,12]

- 1. In cases where new objects are formed inheriting from more than one base class, if two base classes have the same function, the inherited class cannot resolve to which base class it has to map that function.

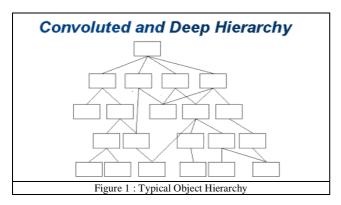

- 2. The object hierarchy is too complex for the developer. For example, sometimes the MFC object hierarchy is too confusing to the developer. A typical complex object hierarchy is shown in Fig. 1.

- 3. The encapsulation of objects is not perfect. The object details are not encapsulated. The inherited object should know everything about the base class along with its full hierarchy for using it. We are giving extra information to the user in this technology. Giving more information than necessary to the user is against abstraction and information hiding principles and is not advisable in any technology.

- 4. One more problem is that the objects do not have a common root and the C++ object hierarchies form a disjoint set of trees.

- 5. We have no solution to handle an unknown objet problem. That means, we cannot hold or perform even a minimum set of operations on an object for which information is unknown.

- 6. It is difficult to expose the behavior across process boundary

It is difficult to divide any task into independent modules. Tightly coupled modules will enforce restrictions on extendibility of the modules. If modules are loosely coupled, they can be designed and extended independently, without affecting other modules. There are several such problems, for which there is no solution in direct Object Oriented Technology. Today's Component Object Model is providing solutions to such problems. The COM technology is also an object-oriented technology. The COM object is also a C++ object, but the way it manages the data and behavior is entirely different. It adopts several

design patterns to solve above problems. Microsoft provides several frameworks to implement these solutions.

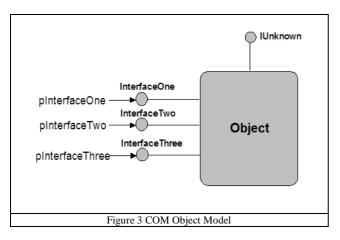

Though it provides solutions to many of the problems, it is too costly to manage. The COM object is not a single object; it is a set of objects. A set of interfaces it supports represents the behavior of a COM object. The COM object encapsulation is perfect. It hides entire object including the object source, object hierarchy and object name. Without knowing even the name of the object, one uses the COM object.

The modules in COM based applications are loosely coupled. They communicate through a set of interfaces, which the components of the module support. The components are assembled with a set of interfaces. COM does not support inheritance. The COM aggregation of components will do the job of inheritance in a more effective way. Aggregating existing components forms new components.

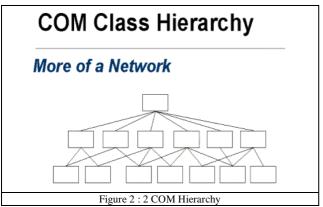

The Hierarchy of Component Technology is simple. Fig. 2 presents a typical COM object hierarchy. Unlike C++ objects, all COM objects belong to the same family. The COM Hierarchy is a simple tree of depth two. All the COM objects and their interfaces are inherited from the common interface known as IUnknown interface. A Typical COM object is presented in the Fig. 3.

# III. FEATURES OF COMPONENT TECHNOLOGY

The COM Concept of Ownership: The COM technology introduces the concept of the ownership subsystem. Each component has an owner. The owner of a component is also a component. A component may be owner of more than one component, but each component has only one owner. Any COM object without an owner is not treated as a full-fledged component. Such components cannot participate in aggregation and other activities of the software environment under consideration. A few special types of components with a specific purpose are without the owner. A class factory object of a COM object has no owner as it is given a special purpose of implementing a design pattern, namely 'Class Factory', which is a creational pattern, the intent of which is to create components in a uniform way through system registry without class name, server location and the type in which component it is implemented.

The owner of a component has full control over the component. A pointer to IUnknown interface of the owner component is stored along with the COM object. A component can become owner of itself but the owner IUnknown interface should not be null.

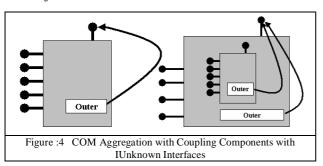

Fig. 4 presents two COM objects with owners. The first COM object holds its own IUnknown interface. In this case, it is owner of itself. The second COM object has an aggregated COM object in it. The owner of the aggregated COM object is the outer COM object. The outer object also should have an owner. In this case the outer object is the owner of itself. When we query an interface on any component, it will pass the call to the outer object, which is the owner of the object. The outer object also passes the call again to its owner. Finally, the call will reach the owner itself. When we query on the IUnknown interface of internal interfaces, the call will never pass the outer-object. If IUnknown is passed, the system will collapse as ownership gets collapsed, spoiling internal integrity and security.

The IUnknown interface alone can make the object unloaded, by making the interface count zero. That is why, the IUnknown is known as the controlling interface. These concepts will play an important role in the COM aggregation. The IUnknown interface is hidden within the outer-object. This is not given to the other components or procedures. This is as powerful as a pointer to the object.

COM object is a set of assembled components, but the user views it as a single object. Entire internal management is encapsulated through these concepts. Loading, managing

and unloading the inside components are the jobs of the outer object.

TABLE I IUnknown Interface format

The definition of IUnknown interface is presented in Table 1.

- i) The m\_cRef means reference count to represent number of objects using the components. Once the count is zero, the object gets deleted automatically.

- ii) The AddReff increases the reference count when the new client objects start using the object and decreases the count when it is released.

- iii) When the object under the service leaves the component, automatically the count will be decreased; otherwise memory leak and runtime error crash the system. These are major problems in Component based systems.

- iv) Query Interface of any Interface can ask other Interfaces from the Component for further use with the Interface ID. Depending on the permission, it releases in a systematic way unlike simple objects for which the number of clients is not known.

#### The COM Aggregation:

The Components cannot be inherited; as they are windows objects and they are registered objects. The name and location of the header file and server is not known to the client. The COM technology reuses the component using a special technique known as aggregation. The COM aggregation is managed in several ways depending up on the requirement. The way of managing the aggregated object will decides the type of aggregation.

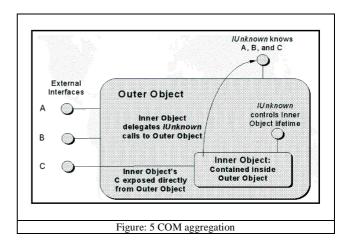

- i) Fig. 5 presents a typical COM aggregation. In this, the outer object delegates all the queries to all the aggregated objects in a specified order without seeing the queried interface. This is known as perfect delegation.

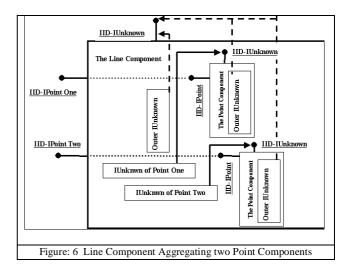

- ii) Fig. 6 presents another type of COM aggregation. The Line object aggregates two point components. The Line query interface function will decide to which object it has to pass the query.

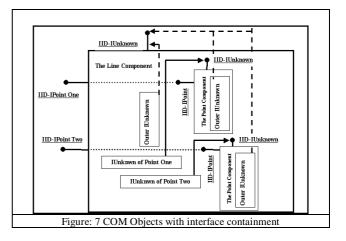

iii) Fig. 7 presents the COM technique of interface containment. The COM technology uses containment for overwriting the behavior. The outer object will reimplement the interface, which is available in the aggregated object.

# IV. FEATURES OF COMPONENT DEVELOPMENT PROCEDURES AND CONCETS

The component development process is complex compard with simple OOP based C++ application, but it has lots of features that solve several client requirements. The OLE features like cut and past, in place activation, drag and drop, container and server, and several modern requirements are possible only with this technology. As a consequence, often IT industry is forced to adopt these procedures. The steps required to build a simple Beeper object are as follows:

- i) The beeper in a direct application needs a single class and a single application to give a beep sound for the given client input signal. In Component model several project and directories are required in a particular hierarchy; the files need to be shared across several projects. Sample files SRC (source files), INCLUDE (for header files), project files, Registration files for registry entry, INTERFACE files for interfaces, BIN for application's executable files (EXE) and DLL for server dynamic link libraries components.

- i) The component needs a GUID globally unique ID generated by a special application of Microsoft, namely guidge.exe which generates a unique ID which will be unique across the world. An ID generated once will never get generated again so that Components and interfaces are referred with that ID. If two GUIDs match in any system totally, Windows under use will crash as shown in Table 2.

- ii) IDL and ODL files with Interface Description language and Object Description language scripts are used to build automation layer so that functionality is exported to VB application. Compilation of this script gives header file to C++ and type library to VB layer. This exports C++ functionality to VB application.

- iii) Microsoft provides various wizards for generating all these facilities automatically for unknown clients.

#### SAMPLE GUID FILE

```

#ifndef _H_GUID

#define _H_GUID 1

#include <windows.h>

#include <objbase.h>

// {765BFF32-C207-11d0-BC7B-080036603003}

DEFINE_GUID(CLSID_CBeeper, 0x765bff32, 0xc207, 0x11d0, 0xbc, 0x7b, 0x8, 0x0, 0x36, 0x60, 0x30, 0x3);

#endif // _H_GUID

```

iv) The sample procedure to crate a beaper object throught system registry and class fatory presented in Table 3.

#### TABLE III COM OBJECT CREATION CODE

```

STDMETHODIMP CBeeperClassFactory::CreateInstance

(LPUNKNOWN punkOuter,

REFIID riid, LPVOID FAR *ppvObj)

CBeeper*

pObj;

HREŜULT

hr:

*ppvObj = NULL;

hr=ResultFromScode(E_OUTOFMEMORY);

if \ (NULL \ != punkOuter \ \&\& \ !IsEqualIID(riid, IID_IUnknown)) \\

return ResultFromScode(E_NOINTERFACE);

pObj = new CBeeper(punkOuter);

if (NULL == pObj) return hr;

if (pObj->Initialize())

hr = pObj->QueryInterface(riid, ppvObj);

if (FAILED(hr))

delete pObj;

else ServerIncrementNumberOfObjects();

return hr;

STDMETHODIMP_(ULONG) CBeeper::AddRef(void)

return ++m_cRef;

STDMETHODIMP_(ULONG) CBeeper::Release(void)

ULONG cRefT;

cRefT = --m_cRef;

if (!m_cRef) {

delete this;

ServerDecrementNumberOfObjects();

return cRefT;

```

# VI. COMPONENT BASED GRAPHIC FRAMEWORKS

The Component Technology builds an application environment to provide techical services to client requirements and providing resources without concern to either application domain or funtionality. It provides a communication environment that provides a session to enable client and server to do busness. The same procedures provided in this will be applicable in several requirements and application domains.

The major components of any project environment are client and server. Different types of servers in use are 'In process servers'. They support and provide services through DDLs, local servers, and work in different processes but on same system. The local server works on the same network connected systems to distribute and share services to enable different systems of the same network to share services. An example of this is the DCOM of Microsoft.

New frame works provide several advanced technological features of communicating over Internet based protocol, for examples Simple Object Access Protocols (SOAP), Web services, mobile communications etc. All these Technologies can work like wrappers. The code and traditional technologies still work. Several Wizards are available to the developer for using all these techniques. These Technologies and wizards are little costly and complex. Developer will never get total control

over internal procedures though they decrease the development time and cost of development.

Several layers and code models of development of a Graphic framework and code segments are presented in this section without functional models. The functional design concepts are presented in [1]. Without using code, COM enables all these object oriented graphic frameworks to be exported to VB layer or other web based or mobile based technologies through wizards. But user will never get total control over the requirements for configuration other than using them.

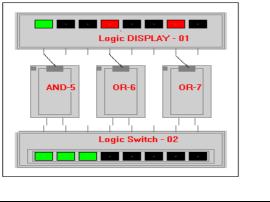

i) The framework is a layered development. All the basic functions required should be developed as libraries, classes and generic object oriented frameworks [1,3]. For the domain considered, dynamic display files are used to simulate several graphic systems like Logic circuits, Printed circuit boards, Debugger driver tools using dynamic display files, shown in Table 4 show sample application oriented functional components [1].

### TABLE IV(a) DISPLAY ALGORITHMS LIBRARIES

# TABLE IV(c): COMPONENT SEMANTIC DEFINITION FOR AN ELECTRONIC DISPLAY LID COMPONENT

```

void VRLogicLID(Component* ge)

{// Component color

ge->SetLineColor(ge->GetBkColor());

ge->RectSolidAt(0,0,100,100);

// Inside Area

ge->SetLineColor(LIGHTGRAY1);

ge->RectSolidAt(0,0,96,96);

ge->SetLineColor(DARKGRAY1);

// Designing light on/off status

int k=1:

for (int i=-35; i<=35; i+=10)

if (ge->GetData(k)==1)

ge->SetLineColor(RGB(0,255,0));

else if (ge->GetData(k)==0)

ge->SetLineColor(RGB(255,255,255));

else if (ge->GetData(k)==2)

ge->SetLineColor(RGB(255,0,0));

else

ge->SetLineColor(RGB(0,0,0));

// 255,255,255 is white(0 or OFF)

// all zeros black (junk data)

// 255 ,0,0 is red(error in output)

```

```

//0,255,0 is green(1 or ON)

ge->RectSolidAt(12,i,15,8);

ge->SetLineColor(RGB(0,0,0));

ge->RectAt(12,i,-15,8);

k=k+1:

ge->SetLineColor(DARKGRAY1);

for(int i = -35; i <= 35; i += 10)

ge->MoveTo(-45,i);

ge->LineRel(-15,0);

}// displaying pins of the component

// displaying text of the components

ge->TextBkColor(LIGHTGRAY1);

ge->TextColor(RGB(255,0,0));

ge->TextAt(-40,25);

ge->Text11At(-40,-25);

} // end of the procedure

TABLE IV(d) :

INTERFACE IDisplayFileInstructions

class IDisplayFileInstructions

```

void virtual TextColor(COLORREF col) = 0;

void virtual Text11At( int x,int y) = 0; // 15 Text

ii) The COM needs to define interfaces and COM environment to export these components over application environment to the client through proper channel as per permissions and requirements, as shown in the following sample code segments in Table 5.

TABLE V: TYPICAL GRAPHIC INTERFACE

```

#undef INTERFACE

#define INTERFACE IGPersist

DECLARE_INTERFACE_(IGPersist, IUnknown)

{

STDMETHOD(QueryInterface) (THIS_ REFIID riid, LPVOID FAR

*ppvObj) PURE;

STDMETHOD_(ULONG, AddRef)(THIS) PURE;

STDMETHOD_(ULONG, Release)(THIS) PURE;

STDMETHOD_(Serialize)(THIS_ CArchive &ar) PURE;

STDMETHOD_(CLSID,GetClsid) (THIS) PURE;

};

typedef IGPersist FAR* LPIGPersist;

```

iii) The class and Interface ID models are presented in table 6

#### TABLE VI THE CLASS INTERFACE GUIDS AND REGISTRATION FILE MODEL

```

REGEDIT

HKEY_CLASSES_ROOT\CLine = CLine Object

```

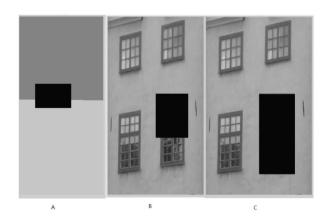

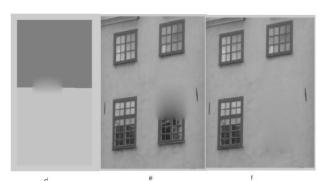

#### vi) Pattern Frames to mke COM procedures simple

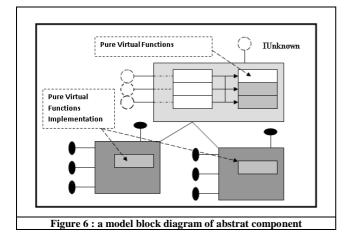

The development procedure of adding components from the frame work need to follow entire COM procedure. For this purpose, the following Abstract COM pattern framework is useful. [4]. Fig. 6 shows a block diagram of abstract component which enables the developer to use COM component like a simple C++ object without complex procedures and with Component features.

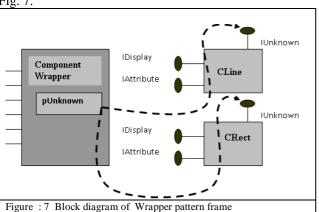

The VC client can use the framework like a simple object oriented framework using wrapper object as shown in Fig. 7.

TABLE VII MODEL WRAPPER DEFINITION

```

#ifndef HGraphicElement

#define HGraphicElement 0

#include <objbase.h>

#include "IGraph.h'

#include "Guid.h'

#ifdef HGraphicSERVER

class __declspec( dllexport ) HGraphic

class __declspec( dllimport ) HGraphic

#endif

private:

LPUNKNOWN

m_IUnknown;

LPIGPersist

m_IPersist;

LPIGAttributes

m_IAttributes;

LPIGDisplay

m_IDisplay;

LPIGEdit

m_IEdit;

LPIGLocate

m_ILocate;

public:

HGraphic(CLSID);

~HGraphic();

HRESULT Serialize(CArchive &ar);

CLSID GetClsid(void);

HRESULT SetPoints(ULONG,ULONG,ULONG,ULONG);

HRESULT GetColor(void);

HRESULT SetName(CString);

CString GetName(void);

HRESULT GetName(CString* );

}

```

The Visual Basic can extract services from automation layer through wizards and ODL and IDL file outputs.

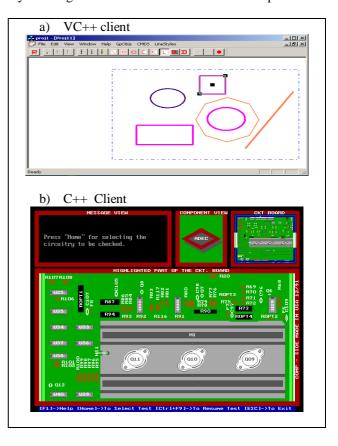

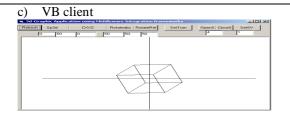

d) Semantic logic application in VC++ in dot net 2010

Figure 8 : Graphic application outputs of the framework

A simple visual base code to use server through wrapper objects and wizards is presented in Table 8.

#### TABLE VIII SAMPLE VB CLIENT CODE SEGMENT

Private Sub Command1\_Click ()

HGP3D1.Sp3d Text1.Text, Text2.Text, Text3.Text, Text4.Text

End Sub

Private Sub Command10\_Click ()

HGP3D1.S1

End Sub

Private Sub Command11\_Click()

HGP3D1 S2

End Sub

Private Sub Command4\_Click()

HGP3D1.RoteteSegmentAbs Text7.Text, Text4.Text, Text5.Text,

Text6.Text

HGP3D1.ShowAll

End Sub

#### **CONCLUSIONS**

The component based frameworks, their processes, advantages, problems and features, various processes to make implementation simple, sample graphic application code segments, and outputs of several sample applications have been presented. Details of models are described in some of the papers in references, as indicated at various places in the paper. It is suggested that same procedures can be applied to other domains for the development of the framework for the other domain environment not concerned with domain or application requirements. The

application presented can be treated as a model for demonstration of environment. Several wizards are available to pack the Object Oriented Frameworks. They can be used for exporting into new technical environments, but clients will not get total control over configuring the requirements and use totally Component features. The user can use only assigned or permitted services. So implementing core Component features as per layers is advised. Using and developing new pattern frames to make use of Component Technology is also advised.

#### REFERENCES

- [1] Dr.Hari Ramakrishna, "Managing semantic of graphic components through remodeling traditional display files", Journal of Science & Technology Journal, Volume VII, June 2014 ISSN 2277-3916

- [2] Dr.Hari Ramakrishna, "A pattern language and traditional programming practices for exporting functionality" CVR Journal of Science & Technology, released in December 2013 ISSN 2277-3916

- [3] Dr.Hari Ramakrishna, "Pattern Approach to Build Traditional Graphic Frame works", International 1 Journal of Computer Applications Volume 59– No.15, p35-42, December 2012. Published by Foundation of Computer Science ISSN:(0975 – 8887), New York, USA

- [4] Dr. Hari Ramakrishna, "Design Pattern for Graphic/CAD Frameworks", Ph.D thesis submitted to Faculty of Engineering Osmania University March 2003,

- [5] Christopher Alexander, "An Introduction for Object-oriented Design", A lecture Note at Alexander Personal web site www.patternlanguage.com

- [6] Hari: Dec 2000 Hari RamaKrishna "COM as new Object Oriented Technology", Proceedings of CSI conference, December 2002 at Visakapatnam.

- [7] Hari RamaKrishna "COM Applications for Real time Electrical Engineering Applications" IEEE sponsored International Conference at Bangalore - 2000.

- [8] Hari Ramaakrishna, "COM based CAD" Proceedings of International Conference on xxx, July 2000 at Jaipure, India

- [9] Hari RamaKrishna "Application of computer graphics in interior design" Proceedings of Conference 1998 at Institutes of Engineers At Hyderabad.

- [10] Hari RamaKrishna "Generation of flooring and wallpaper patterns using computer graphics" Proceedings of the First National Conference on Computer Aided Structural Analysis and Design, Jan 3-5,1996, Engineering Staff College of India and University College of Engineering, Osmania University, Hyderabad

- [11] Hari RamaKrishna, "Object Oriented Graphic Frameworks", International Journal of Engineering Research & Technology, Vol.2 - Issue 1 (January - 2013) e-ISSN: 2278-0181 This work is licensed under a Creative Commons Attribution 4.0 International License.

- [12] Erich Gamma, Richard Helm, Ralph Johnson, and John Vlissides, "Design Patterns: Elements of Reusable Software Architecture", Addison-Wesley, 1995

# Using Domain Ontology and Sequential Rule Mining for Extracting Behavior Patterns from Web Navigation Logs

C. Ramesh<sup>1</sup>, Dr. K. V. Chalapati Rao<sup>2</sup> Dr. A. Govardhan<sup>3</sup>

<sup>1</sup>Department of CSE, CVR College of Engineering Hyderabad, India

Email: hmcr.ramesh@gmail.com

<sup>2</sup>Department of CSE, CVR College of Engineering, Hyderabad, India

Email: chalapatiraokv@gmail.com

<sup>3</sup> Department of CSE, School of Information Technology, JNTUH, Hyderabad, India

Email: govardhan\_cse@yahoo.co.in

Abstract: Due to unprecedented growth of information on the Web and lack of structure in many Web sites, it became real challenge to the Web users to find relevant information. To solve this problem, Personalization becomes a popular solution to customize the World Wide Web environment toward the user's preferences. Recent studies show that Web Usage Mining plays an important role in designing recommendation systems. Classical Web Usage Mining does not take Semantics Knowledge into pattern discovery and recommendation process. Recent studies show that Ontology as domain knowledge can improve pattern's quality. Our work aims to incorporate semantics knowledge into Web Usage Mining process. ERMiner, a state-of-the art algorithm for Sequential rule mining is applied over the Semantic space to generate frequent Sequential rules. Experimental results shown are promising and proved that incorporating Semantic Knowledge into Web Usage Mining process can provide us with more quality patterns which consequently make the recommendation system more functional, smarter and comprehensive. The experimental results of our Web recommendation system show a significant improvement on the quality of the recommendations.

Index Terms—Web Usage Mining, Semantic Web, Sequential Rule Mining, Ontology, Semantic Web Usage Mining, Web Personalization, Recommendation System.

#### I. INTRODUCTION

With the explosive growth of information on World Wide Web, it has become a real challenge for Web users to access relevant information. One possible approach to solve this problem is Web Personalization [1]. Web personalization [2] is the process of customizing a Web site to the needs of each specific user or set of users, taking advantage of the knowledge acquired through the analysis of the user's navigational behavior.

Web recommender system is a specialized personalization system. Understanding the information needs of users has become a crucial task for Web site owners on the Web. A key requirement in developing successful personalized Web applications is to build user models that can accurately represent users interests and preferences. In addition to the above feature, it has to be machine-understandable and machine- processable.

Though user needs may be elicited in many ways, Usage mining of Web logs is a widely used alternative for understanding usage patterns. However conventional Web usage based recommender systems are limited in their ability to use the domain knowledge of the Web application and their focus is only on Web usage data. As a consequence, the quality of the discovered patterns is low. These patterns do not provide explicit insight into the user's underlying interests and preferences, thus limiting the effectiveness of recommendations as well as the ability of the system to interpret and explain the recommendations [3].

Recent studies[4] hint that Ontology which is an explicit representation of the domain knowledge of the application, if integrated with Web Usage Mining, can enhance the quality of generated usage patterns and help in developing effective Recommendation system.

The combination of Web Usage Mining and Semantic Web has created a new and fast emerging research theme – Semantic Web Usage Mining [5].

The key contributions of our work can be summarized as follows:

- 1) Feeding domain Ontology into Web Usage Mining Process to extract Sequential navigational patterns.

- 2) A state-of-the art algorithm ERMiner, is used in the Sequential rule mining process to generate frequent Sequential rules.

- 3) Generated Sequential rules have antecedent and consequent as sequence of ontological instances instead of mere page views.

The rest of the paper is organized as follows: in section II we review recent advances in Semantic Web Usage Mining research. In section III proposed model and architecture is discussed. Experimental set up and Performance evaluation of the proposed model is presented in section IV. Finally section V provides the concluding remarks and sheds light on future enhancements.

#### II. RELATED WORK

Web Usage Mining is the process of extracting navigational patterns by applying data mining techniques on Web log file. In recent years, Web Usage Mining techniques such as Clustering, Association rule mining, Sequential pattern mining were employed in extracting

navigational patterns and using those patterns in recommendations [4,5]. An extensive literature on Web Usage Mining based recommendation systems is available in [6,7,8]. However the amount of work presenting the combination of Web Usage Mining and Semantic Web is very limited. Work presented by Stumme et al. [9] and Oberle et al. [10] is regarded as first contribution towards the Semantic Web Usage Mining. The authors have sketched out the benefits of combining Semantic Web and Web Mining. The first part of the work is on extracting semantics from Web page. The second part is on the improvement of Web Usage Mining by using Semantics structures in the form of Ontology. Bamshad Mobasher et al. [11] proposed a unified framework based on Probabilistic Latent Semantic analysis to create user models taking into account both usage data and web site contents. The work presented by stumme et al.[12] sketeched different possibilities of combining Semantic web and Web Mining. In a recent work [13], Nasraoui et al, proposed a Web Usage Mining Framework for mining evolving User Profiles of dynamic Web sites by exploiting the external ontology, used for mapping and relating dynamic Web pages. Eirinaki et al [3], presented a system, SEWeP which integrates the Web usage logs with the semantics of Web site's content to improve the personalization. The innovative feature of the architecture was C-logs, an extended form of Web usage log which encapsulates the site semantics. But the framework was limited only to concept hierarchy. Amit Bose et al, [15] proposed a framework for personalization combining usage information and domain knowledge based on ideas from bioinformatics and information retrieval. Vanzin et al.[16] present ontology - based filtering mechanisms for retrieval of Web Usage patterns and the studies presented by Mehdi et al. [17] proposed a framework XPMiner, which mines frequent patterns over ontology based pattern space. The studies assume that meta data of the web page contents can be typically organized into domain ontology and can be used in frequent pattern mining task. The authors have emphasized the importance of semantic relations in the Mining task.

In summary all the above studies attempted to improve the quality of the navigational patterns and subsequently the recommendations by integrating Semantics into Mining tasks. But the content domain ontologies concerned in the above studies share a common limitation. They invariably represent concept taxonomies. Recent approaches which use Semantics knowledge in the form of ontology for extracting behavior patterns from Web navigation logs are presented by Mabroukeh et al. [18] and Yilmaz et al. [19]. Julia Hoxha et al. [20] presented an approach for the Semantic Formalization of Web browsing behavior across multiple sites. The Usage logs are mapped to comprehensive events from the application domain.

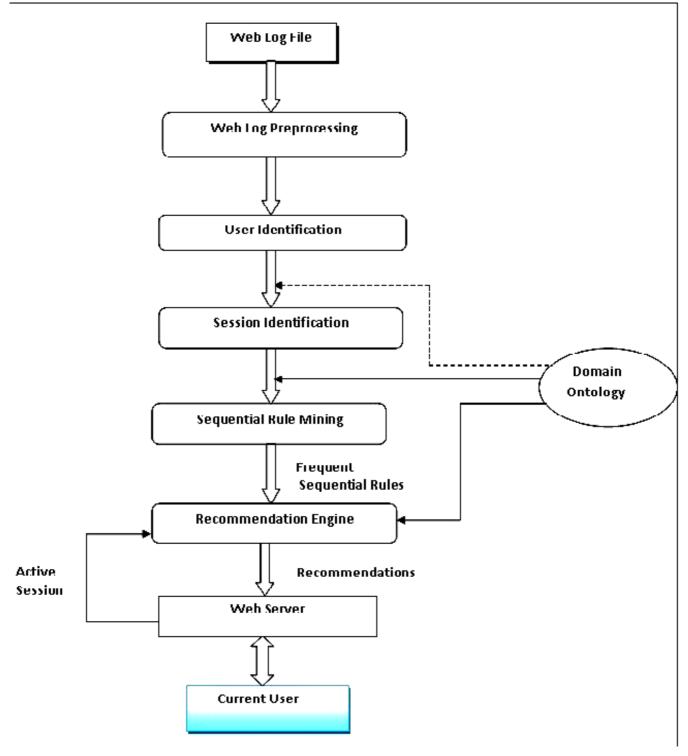

#### III. PROPOSED SYSTEM

The proposed system has extended the classical Web Usage Mining system. It includes the basic steps such as data acquisition, data preprocessing, extraction of

Semantic frequent Sequential rules and Web page recommendation. Web Log file forms the main basis of input to the Web Usage Mining process.

#### A. Data Preprocessing:

Data preprocessing phase includes data cleaning, user identification, and session identification. This task along with Sequential Rule Mining task is implemented as offline phase. Generally several preprocessing tasks need to be performed on the Web access database before user navigational patterns are extracted. Due to large amount of irrelevant information in the Web log file, raw usage data need to preprocessed by applying preprocessing techniques and converted into sequential database.

Initially the usage data logs are centrally stored in raw form as produced upon user interaction. We regard each log record as a browsing event. Log files are pruned to remove the non-responded Web requests and also the requests made by software agents such as Web crawlers, and bots are eliminated. The browsing events are grouped into sessions based on user's IP address. Then the browsing events are formalized into Semantic form by mapping the URLs into respective RDF form. The formalized browsing events obtained constitute a semantic rich user model and form the basis of the Semantic Web Usage Analysis.

#### B. Ontology Construction:

An Ontology is defined as "an explicit specification of a conceptualization" [21]. A conceptualization consists of a set of entities (such as objects and concepts) that may be used to express knowledge and relationships. Protégé [22] tool is used for constructing and editing the ontology of the Web application. The Semantic Web Dog Food (SWDF) [23] and DBpedia Ontology [24] are available publicly. OWL and RDF are the popular Semantic Web technologies used in representing Ontology.

#### C. Sequential Rule Mining:

After preprocessing step, Web access sequence database, consisting of a sequence of page views is obtained. Since the RDF representation of the web resources for SWDF and DBpedia datasets are available, the ontological instances of the objects of the browsing events are obtained. We employed the procedure presented in [20] for Semantic formalization of browsing events. And further frequent Sequential rules are generated by applying Sequential rule mining.

In the proposed system, we preferred Sequential rule mining over Frequent Pattern Mining, since the sequence information in the navigation is retained in the generated rules. In the Proposed System, ERMiner (Equivalence class based Sequential Rule Miner) [25] algorithm is employed to generate Frequent Sequential rules. It relies on a vertical representation of the database to avoid performing database projection and adopts the novel idea of exploring the search space of rules using equivalence classes of rules having the same antecedent or consequent.

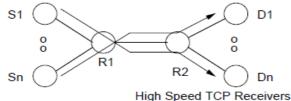

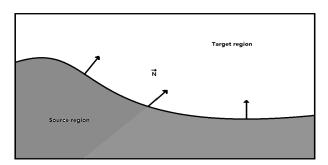

Figure 1 : An Architecture for Online Recommendations using Web Usage Mining and Domain Ontology

SPMF [26] is an open source data mining framework implemented in Java. For extracting frequent Sequential rules we have implemented ERMiner algorithm using this framework.

#### D. Generating Recommendation

In recommendation phase, Sequential rules extracted in the above process and active user's navigation session are compared in order to recommend a new page or pages to the user in real time.

Generally, not all the Web pages in the active session path are taken into account while generating a recommendation set. Window count, a parameter which defines the maximum number of previous page visits to be used while generating a recommendation set to the current user is defined.

The recommendation set constitutes the set of Sequential rules which will be used for generating recommendations. After constructing the recommendation set, the Web Page recommendation begins. The Sequential rules in the recommendation set are ordered by their confidence value and the highest one is taken first for the recommendation. For each Sequential Association rule in the recommendation set, its consequent part is extracted and used for recommending Web resources. The ontological instances of consequent part are reverse mapped to page views before applying recommendation

# IV. EXPERIMENTS AND PERFORMANCE EVALUATION

#### A. DataSet Description:

Experiments were conducted on two publicly available real datasets SWDF (Semantic Web Dog Food) and DBpedia. SWDF is a very active Web site of publications, people and organizations in the Semantic Web fields, covering several of the major conferences and workshops. DBpedia is shallow, cross domain ontology representing the Wikipedia information in structured format ie.. in the form of classes and properties.

TABLE I

THE SUMMARY STATISTICS OF THE EXPERIMENTAL DATA

SETS.

|                 | SWDF            | DBpedia         |

|-----------------|-----------------|-----------------|

| #sessions       | 890             | 1020            |

| Avg             | 150             | 187             |

| #sessions/day   |                 |                 |

| #triples        | 27790           | 34870           |

| Period of Usage | 17-07-09 to 22- | 21-04-11 to 26- |

| data            | 07-09           | 04-11           |

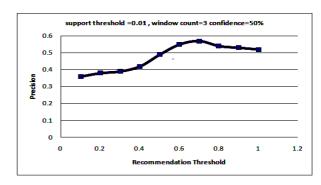

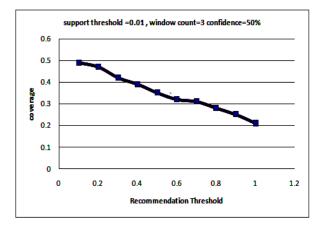

#### B. Evaluation:

To evaluate the performance of our system we have employed the evaluation metrics discussed in [27]. We have used the measures such as precision and recall. As precision and coverage are inversely related, a combination measure called the F1-measure giving equal weight to both precision and coverage can also be used. Precision measures the degree to which the recommendation engine produces accurate recommendations. Coverage measures

the ability of the recommendation engine to produce all of the pages that are likely to be visited by the user.

10—fold cross — validation is performed on each of the datasets. Each session t in the test session set ts is divided into two parts. The first n web pages of test session are used for generating recommendations, and the second part is simulated as the future requests (page visits) which are compared with the output of the recommendation system. w is called the window count, which represents the last n pages in the first part of session called active session window (asw).

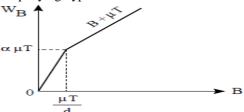

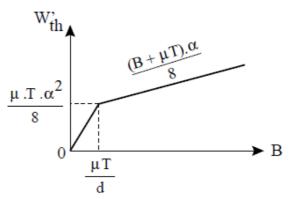

The recommendation engine takes *asw* and the recommendation threshold  $\mu$  as the input and generates a recommend list which is denoted by  $Rec(asw, \mu)$ . Note that  $Rec(asw, \mu)$  contains all pages whose recommendation score is at least  $\mu$ . The set of pages  $Rec(asw, \mu)$  can now be compared with the remaining |t|-n, pages in t. We denote this portion of t by Eval.

Precision (Rec(asw,

$$\mu$$

) =

$$\frac{\left| \text{Rec}(\text{asw}, \mu) \cap \text{Eval} \right|}{\left| \text{Rec}(\text{asw}, \mu) \right|}$$

Coverage (Rec(asw,

$$\mu$$

) =

$$\frac{\left| \text{Rec}(\text{asw}, \mu) \cap \text{Eval} \right|}{\left| \text{Eval} \right|}$$

We performed experiments with recommendation threshold ranging from 0.1 to 1.0.

The results of these experiments are given below.

Figure. 2: Recommendation Precision

Figure.3: Recommendation Coverage

#### V. CONCLUSIONS AND FUTURE WORK

The proposed work extracts interesting Sequential rules using Semantic Web Usage Mining. We have applied an extended version of the state-of-the art Sequential rule mining algorithm ERMiner over Ontological space to extract frequent and interesting Sequential rules. The generated Sequential rules are in terms of ontological instances instead of Web page views. The discovered Semantic Sequential rules form the basis of recommendation engine of the proposed model. Compared with the recommendation system based on classical Web Usage Mining, our proposed model shows promising results.

Experimental results are promising and we believe that the successful integration of Semantic knowledge with Web Usage Mining is likely to lead to the next generation of Personalization tools which will be more intelligent and more useful for Web Users.

Future work includes the development of techniques related to the acquisition of domain ontology, when this is not provided, since it is a crucial component of the Semantic enrichment of usage data with concepts from the application domain. Proposed work can also be extended by combining the clustering and sequential rule mining techniques incorporating domain ontology, making a hybrid recommendation system.

#### **REFERENCES:**

- M. Eirinaki, M. Vazirgiannis, "Web Mining for Web Personalization", ACM Transaction on Internet Technology. Vol. 3(1), pp.1-27, 2003.

- M. Eirinaki, M. Vazirgiannis and I. Varlamis, (2003) "SEWeP: Using Site Semantics and aTaxonomy to Enhance the Web Personalization Process", *Proc. of the 9th SIGKDD Conf.* 2003.

- C.Ramesh, K.Chalapati Rao, A.Govardhan, "A Semantically Enriched Web Usage Based Recommendation Model", International Journal of Computer Science and Information Technology (IJCSIT), vol.3,no.5, pp.193-202.

- 4. B. Zhou, S. C. Hui, and K. Chang, "An intelligent recommender system using sequential Web access patterns," in IEEE conference on cybernetics and intelligent systems, pp. 393–398,2004.

- Sarabjot Singh Anand and Bamshad Mobasher, "Intelligent techniques for Web Personalization", LNCS,vol.3169, Springer, 2005.

- B.Mobasher, R.Cooley, J.Srivastava, "Creating Adaptive Web Sites through Usage-Based Clustering of URLs", In proc. of the IEEE Knowledge and Data Engineering Exchange Workshop (KDEX'99), November 1999.

- Bamshad Mobasher, Robert Cooley, and Jaideep Srivastava, "Automatic personalization based on Web usage mining,"Communications of the ACM, vol. 43, no. 8, pp. 142–151, 2000.

- 8. M. Perkowitz, O.Etzioni, "Adaptive Web Sites: Conceptual Framework and Case Study", In proc. of WWW,1999.

- B.Berendt, A. Hotho and G. Stumme, (2002) "Towards Semantic Web Mining", Horrocks, I., Hendler, J. (eds.) ISWC 2002, LNCS, Vol. 2342, pp. 267-278, Springer, Heidelberg (2002).

- D.oberle, B.Berendt , A. Hotho, and J. Gonzalez, " Conceptual User Tracking". In E.M. Ruiz , J.Segovia , and

- P.S. Szczepaniak, editors , AWIC ,volume 2663 of Lecture Notes in Computer Science, pages 155 164,springer , 2003.

- Xin Jin, Yan Zan Zhou and Bamshad Mobasher, "A unified Approach to Personalization Based on Probabilistic Latent Semantic Models of Web Usage and Content." In AAAI workshop on Semantic Web Personalization(SWP'04), July 2004.

- 12. G.Stumme, B. Berendt and A Hotho, (2004) "Usage Mining for and on the Semantic Web", *Data Mining: Next Generation Challenges and Future Directions*", pp. 461-480, AAAI/MIT Press.

- O.Nasraoui, Maha Soliman, Esin Saka, Antonio Badia and Richard Germain, (2008) "A Web Usage Mining Framework for mining evolving user profiles in dynamic Web sites", *IEEE Trans. Knowl. Data Eng.* Vol. 20, No. 2, pp. 202-215.

- R.Agrawal and R. Srikant, "Mining Sequential Patterns", In proceedings of the 11<sup>th</sup> International Conference on Data Engineering.pp 3-14, Taipei, Taiwan, 1995.

- Amit Bose, Kalyan Beemanapalli, Jaideep Srivastava and Sigal sahar, (2006) "Incorporating Concept hierarchies into Usage Mining Based

- M. Vanzin, K. Becker, and D. D. A. Ruiz. "Ontology-based filtering mechanisms for web usage patterns retrieval". In EC-Web'05, pp. 267-277, 2005.

- 17. Mehdi Adda, Petko Valtchev, and Rokia Missaoui, "A framework for mining meaningful usage patterns within a semantically enhanced web portal," in Proceedings of the Third C\* Conference on Computer Science and Software Engineering C3S2E '10, New York, USA, 2010, pp. 138-147.

- Nizar Mabroukeh and C.I. Ezeife, (2009) "Using domain ontology for Semantic Web usage mining and next page prediction", Proceedings of the 18th ACM Conference on Information and Knowledge Management (CIKM), Hong Kong, November 2-6, 2009, pp. 1677-1680.

- H.Yilmaz and P.Senkul, "Using ontology and sequence information for extracting behavior patterns from web navigation logs". In Data Mining Workshops (ICDMW), 2010 IEEE International conference on – pages 549-556, dec 2010.

- Julia Hoxha, Martin Junghans, and Sudhir Agarwal, "Enabling Semantic Analysis of User Browsing Patterns in the Web of Datain Julia Hoxha, Martin Junghans, Sudhir Agarwal, Lyon, France, 2012.

- 21. T.Gruber, "Toward Principles for the Design of Ontologies Used for Knowledge Sharing." International Journal of Human Studies. Vol. 43, pp. 907-928. (1995).

- 22. http://protege.stanford.edu/

- 23. http://data.semanticweb.org/ns/swc/swc\_2009-05-09.html

- 24. <a href="http://wiki.dbpedia.org/Ontology">http://wiki.dbpedia.org/Ontology</a>

- Fournier-Viger, P., Gueniche, T., Zida, S., Tseng, V. S., "ERMiner: Sequential Rule Mining using Equivalence Classes." Proc. 13th Intern. Symposium on Intelligent Data Analysis (IDA 2014), Springer, LNCS 8819, pp. 108-119.

- 26. <a href="http://philippe-fournier-viger.com/spmf/">http://philippe-fournier-viger.com/spmf/</a>

- 27. H. Dai and B. Mobasher, (2002) "Using Ontologies to discover domain- level Web Usage profiles", *Proc. of the 2nd Semantic Web Mining Workshop at ECML/PKDD 2002*, Helsinki,Finland, 2002.

# Improving Performance of 802.11n Networks Using Various Rate Adaption Algorithms

D. Arjun Mitra Reddy<sup>1,</sup> B. Prathyusha<sup>2</sup> and D. Amarendranath Reddy<sup>3</sup>

<sup>1</sup>Research Assistant, Department of Computer Science, University of Central Florida, Orlando, Flordia, USA

Email: arjunmitrareddy@gmail.com

<sup>2</sup> Department of Computer Science, State University of New York at Buffalo, New York, USA

Email: bobbaprathyusha@yahoo.com <sup>3</sup>CMRIT, Hyderabad, India

Email: d.amarendranath@gmail.com

Abstract — In a WLAN subject to variable remote channel conditions, rate adjustment assumes a critical part to more productively use the physical connection. Rate adjustment is a MAC-layer instrument in IEEE 802.11 systems to guarantee proficient usage of fluctuating remote channel. Traditional 802.11 rate adjustment calculations depend on input from the recipient to accurately pick a sending rate, commonly as affirmations (Acks). Without such casings, novel strategies are needed for rate choice. In this paper, the accompanying progressed rate adaption calculations are exhibited:

- a. MAC-Layer Loss Differentiation based rate adaption algorithm

- b. High TCP Performance rate adaption algorithm

- c. Video-Aware Rate Adaption For HD Video Streaming

Index Terms—IEEE 802.11, WLAN, Rate Adaption, ARA Algorithm, DCF, Loss Differentiation, Automatic Rate Fallback.

#### I. INTRODUCTION

The utilization of remote neighborhood (WLANs) in homes, work places, and open regions has been spreading rapidly. The overwhelming WLAN benchmarks have been characterized by the IEEE 802.11 working gathering, with their prosperity moved by the Wi-Fi Alliance [1] [2]. Most IEEE 802.11 WLAN gadgets utilize the dispersed Coordination Function (DCF) tagged in the standard [2] to arrange channel by the transporter sensing access with impact evasion . In DCF, when numerous edges are transmitted all the while by distinctive stations, an impact happens, which annihilates all the transmitted casings. To resolve impacts, the stations utilize a twofold opened exponential backoff calculation and retransmission plan. Two right to gain entrance methods are characterized in 802.11 DCF, the default fundamental access and the discretionary RTS/CTS access. Current WLAN items help more than one regulation sorts and information rates. For instance, in 802.11b, 4 information rates, 1 Mbps, 2 Mbps, 5.5 Mbps, and 11 Mbps, are upheld [3]. On the other hand, a higher information rate does not so much yield a higher throughput. When the channel condition is great, a higher information rate gives a higher throughput. In a practical WLAN environment, the channel condition can fluctuate progressively because of multi-way impedance, and developments of stations, and so forth. To oblige diverse channel conditions, rate adjustment (or auto rate) is normally utilized. This is acknowledged by rate adjustment calculations that modify the regulation mode and information rate to upgrade execution when channel condition changes.

Today, features overwhelm Internet activity and by 2015 it is anticipated that about 50% of the feature movement will be 3d or 2d High Definition (HD) [26]. A high portion of HD feature movement will be devoured by clients that get to Wireless Local territory Networks (Wlans) in homes, ventures or open spaces. This vision is energized by two noteworthy engineering patterns. In the first place, late feature streaming innovation benchmarks, for example, H.264/MPEG-4 section 10 AVC [27] lessen HD feature data transfer capacity necessities utilizing Variable Bit Rate (VBR) feature encoding. Second, the IEEE 802.11n [28] WLAN standard offers high remote physical-layer (PHY) information rates (up to 600 Mbps) utilizing Multiple-Input Multiple-Output (MIMO) reception apparatus advances. Notwithstanding these advances, the issue of streaming HD feature in Wlans is a long way from being explained. VBR advances lessen the normal feature streaming rate by effective encoding of moderate moving scenes. On the other hand, the top rate stays high as it is dictated by the full quality encoding of quick movement scenes.

In this paper, for the MAC-Layer based loss differentiation based method, a new auto rate algorithm calledloss-differentiating-ARF (LD-ARF) that is suitable for arealistic WLAN environment where both collision losses and link error losses can coexist is discussed. Its effectiveness is demonstrated through extensive performance evaluations.

For High TCP Performance algorithm, an efficient and practical rate adaptation algorithm called Advanced Rate Adaptation Algorithm (ARA) is proposed and explained in detail. The key idea of ARA is to make use of the RTS control frame as the probe packet. RTS control frame has several characteristics that make it suitable for such use.

Next For HD streaming, VARA, a Video-Aware Rate Adaptation protocol is used, that optimizes wireless channel probing and PHY rate selection by exploiting the VBR streaming rate information of a video. VARA eliminates the channel probing impact on the video stream by scheduling the probes during the low streaming-rate periods. Furthermore, rather than aggressively trying to find the maximum PHY rate supported by the wireless

channel (like all existing 802.11 rate adaptation protocols), VARA selects the most reliable PHY rate that supports the near-future peak streaming rate. To further reduce the probing overhead, VARA monitors the Frame Error Rate (FER) and adapts probing frequency to the measured wireless channel variability.

The organization of the remainder of this paper is as follows. In Section II, a new loss differentiating ARF algorithm is proposed. The new algorithm involves MAC layer changes only. In Section III, several guidelines for designing an efficient rate adaptation scheme for IEEE 802.11 networks are given and explain the proposed algorithm and how ARA is implemented is explaned .In Section IV, the design of VARA and the multiplexing techniques are presented. In Section V, the conclusion of this paper is given.

# II. DESCRIPTION OF LOSS-DIFFERENTIATING ARF ALGORITHM

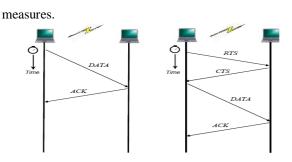

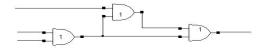

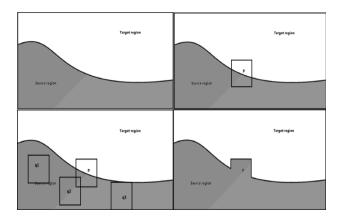

Figure 1. Basic and RTS/CTS access in 802.11 DCF

In this area, firstly, the real idea of this convention is assessed. At that point the LD-ARF calculation, which joins the misfortune separating MAC and the current ARF calculation, is proposed. The following segment will assess its execution.

#### A. Loss Differentiating MAC Protocol

The misfortune separating MAC layer convention is expected as an improvement of the 802.11 DCF. There are two right to gain entrance methodologies in DCF, fundamental and RTS/CTS. Figure 1 delineates the two right to gain entrance techniques. The alteration to the DCF in the new convention includes both essential and RTS/CTS access techniques. RTS/CTS is a noncompulsory emphasize in a 802.11 WLAN and it is helpful when the information casing size is extensive, the quantity of stations is huge, or there are concealed terminals. It is a 4way handshake method as indicated in Figure 1. The misfortune separation system in the RTS/CTS access method is clear and the 4-way message trade grouping is not transformed: (i) If both the CTS and afterward the ACK edges are gotten at the sender, the transmission was effective. (ii) If the CTS edge is gotten however the ACK casing is not, the transmission has fizzled, in all probability because of a connection mistake. (iii) If the CTS edge is not gotten, probably a crash has happened. Since RTS and CTS are short and generally transmitted at a low rate, the misfortune separation can be very powerful. Essential

access is the default get to in 802.11 DCF. It is a two-way handshake method (see Figure 1). As a rule, e.g., when there is no concealed terminal, the default essential access is more effective than RTS/CTS access. The misfortune separation for essential access is not as direct as that for RTS/CTS access. In the first essential access method, just when the got information casing is right, is an input message (ACK) sent. At the point when the got information casing is in blunder, the recipient does not give any reaction. As clarified beforehand, two reasons, i.e., a crash or connection blunders, may cause a mistaken edge gathering in the essential access technique, and the sender can't separate between these misfortune components and take

Thusly, a component must be consolidated so that the recipient can focus the reason for a fizzled gathering and advise the sender. One of the favorable circumstances of the new misfortune separating MAC layer convention is that the change to the standard DCF capacity has been minimized. No alteration to the PHY layer is required. In this way the convention is not difficult to execute.

B. Loss Differentiating Automatic Rate Fallback Algorithm It has been clarified that when an impact happens, the information rate ought not be lessened. In this manner the adjustment to the ARF calculation is that the information rate is decreased just when a loss of information casing is brought about by connection slips

- If an ACK is received (the transmission is successful) or rate-up timer expires, then, counter\_downrate= 0; counter\_uprate++;

If (counter\_uprate≥Nup) {

physical rate is increased; counter\_uprate= 0; rate-up timer is stopped.

}

- If a NAK is received (a link error loss is detected), then,

counter\_uprate= 0;

counter\_downrate++;

If (counter\_downrate≥Ndown) or the rate was just increased

{

physical rate is reduced;

counter\_downrate= 0;

rate-up timer is started.

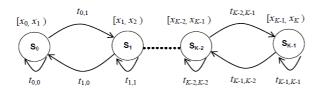

The Gilbert-Elliot channel model has been broadly used to model remote channels subject to blast mistakes. Estimations directed on the remote direct in an IEEE 802.11 WLAN demonstrate that the Gilbert-Elliot model gives a decent expectation of WLAN execution. To assess the execution of the proposed LD- ARF calculation under

variable conditions and contrast and that of the ARF calculation, in this paper an augmentation model of the first Gilbert-Elliot model is utilized. It is a K-state Markov divert display as indicated in Figure 2. In the K-state show, the remote divert could be in one of the K states from S<sub>0</sub> to S<sub>K-1</sub>. In each one state, Si, the relating SNR esteem at each one edge transmission is consistently taken from the scope of [xi, xi+1) db, where xi+1>xi. The visit time in each one state takes after an exponential appropriation (or if discrete time is utilized the comparable Geometric dispersion). This model is truly like the arbitrary walk model, which can be seen as the situation where the two imparting WLAN stations approach and leave haphazardly. In recreations, a 10-state channel model has been utilized. A modestly changing channel model has been viewed as where for each one state, Si,, the normal time span is 1 second, and the move probabilities ti,i-1=ti,i+1. For each one state, Si, the SNR values (in db) are consistently disseminated between [i, i+1]. Accordingly the conceivable SNR qualities created by this model are conveyed between 0 db and 10 db. IEEE 802.11b is utilized as a part of reproductions since it is the most generally utilized WLAN standard by a long shot. Additionally, its physical property has been settled in [11], [12], and [13]. Besides, the Wavelan-II item in which ARF was initially executed has comparable properties to 802.11b1. It is more serious to utilize the control parameter values given in Wavelan-II to analyze the execution of the auto rate calculations. In our reenactments for ARF and LD-ARF, this information rate is essentially circumvent.

In the reproduction situations, all stations are soaked, yet it is accepted that the conclusions got from the reenactment results are pertinent to non-immersed stations also. Expect there is no shrouded terminal and the stations are close enough that when they transmit outlines at the same time, the ensuing impact demolishes the casings included. The information outline payload size is 1000 bytes. The information outline blunder rate, the information outline MAC header lapse rate (HLR), and the control outline mistake rates are dead set individually by their sizes, their rates, and the SNR qualities created from the 10-state channe model when the casing is sent.

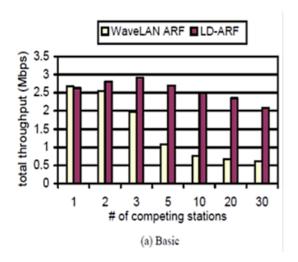

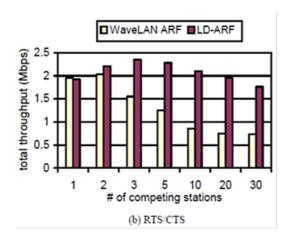

Figure 3. Two Different but performance equivalent WLAN topologies

The MAC header and body parts are transmitted at the same information rate. The essential rates for the control casings take after the principles given underneath. For a RTS outline transmission, its rate is the same as the sending station's information rate for an information outline. For ACK, NAK and CTS, their sending rates are the same as the rate utilized for the got information casing or RTS outline. Note that if the fundamental rate or the header part rate is lower than the information edge rate, the misfortune separating MAC convention can be more powerful. In this manner these settings may not yield the best execution for the LD-ARF. It is going to be demonstrated. The estimation of the rate-up clock was not suggested in [4]. As demonstrated in [7], over a wide range (from a few seconds to around one moment) the rate-up clock esteem does not have a critical effect on execution and the ensuing throughput is equivalent. In our reenactments, we don't put concentrate on this clock and essentially set its esteem to 10 seconds. A circumstance where all the WLAN connections encounter precisely the same channel state in the meantime (Scenario 1) is considered. It can be seen from Figure 3 that when there is stand out connection (i.e., one station sending activity), the two calculations produce comparative throughput. In any case, when there are numerous connections (i.e., various contending stations), the execution of the first ARF calculation debases significantly. At the point when the quantity of connections is 3, the execution change by the new LD-ARF over ARF is extremely noteworthy. At the point when the quantity of contending stations is huge, the new LD-ARF calculation yields more than twofold the throughput of the ARF calculation. In the accompanying situations, more reasonable circumstances where the channel conditions are autonomous are considered. In Scenario 2, each one connection encounters a channel condition that is resolved autonomously from the 10-state channel model. Figure 3 looks at the framework throughput of LD-ARF and ARF for fundamental access and RTS/CTS get to in Scenario 2. Like Scenario 1, when the quantity of contending stations is huge, the throughput change by the new LD-ARF calculation is more than 100%. Indeed so the LD-ARF can attain huge execution pick up over ARF.

Figure 4. Performance Comparision of Auto Rate algorithms-Scenario 1

Figure 5. Performance Comparisons of Auto Rate algorithms-Scenario 2

#### III. DESIGN GUIDELINES AND ARA ALGORITHM

#### A. Design Guidelines:

#### • Ability to Differentiate Frame Losses

In IEEE 802.11 standard, RTS/CTS control casings trade is impaired of course to minimize overhead. Original rate adjustment plans treat all the casing misfortunes as from channel blurring and decline the information rate at whatever point the edge disappointment proportion achieves certain limit. In the event that an edge misfortune is created by impact, diminishing the information rate won't help take care of the issue yet exacerbate it. Lower transmission rate implies longer transmission time and more extensive show range, which will prompt more crashes and hence exacerbate things. A proficient rate adjustment plan ought to have the capacity to separate the casing misfortunes and react in like manner to these diverse reasons.

#### • Ablility to Response to the Variation of Channel Fast

A productive rate adjustment calculation ought to have the capacity to adjust the nature's domain changes quick, generally, the calculation may lose the chance to send the information outline at a higher rate or continue sending the information outline at a high rate where fruitful conveyance is impractical.

#### • A Good Metric to Adjust Data Rate

A percentage of the current rate adjustment plans alter the information rate by checking the continuous achievement and disappointment number. While this strategy is straightforward, it is not precise. As per RRAA, the likelihood to effectively transmit an information bundle taking after ten back to back victories is just 28.5%. What's more the likelihood of a disappointment in an information transmission after two continuous disappointments is just 36.8%. These insights demonstrate that the sequential achievement or back to back disappointment number ought not be utilized as the metric to conform transmission rate. Different plans utilize the sign to clamor proportion (SNR) as the marker to change the rate. Be that as it may, as per Sample Rate [23] and RRAA, SNR is NOT a decent marker of the channel condition and accordingly ought not be utilized as a part of the metric.

#### • Compatibility with Current Commercial Product

A functional rate adjustment plan ought to be good with current business item, which implies IEEE 802.11 standard can't be adjusted. A few existing rata adjustment plans [20], [21], [22] require the alteration of IEEE 802.11 standard and along these lines are not good with current business items. The over four rules provide for us some essential thoughts on the most proficient method to plan an effective and handy rate adjustment plan. The following area will talk about the proposed calculation in point of interest.

#### B. ARA Algorithm

In this area, a productive and down to earth rate adjustment calculation called Advanced Rate Adaptation Algorithm (ARA) is proposed and clarified in subtle element. The key thought of ARA is to make utilization of the RTS control outline as the test parcel. RTS control

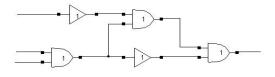

outline has a few qualities that make it suitable for such utilization. To begin with, it is little in size. As per the IEEE 802.11 standard, it is 20 bytes long. Contrasted with an ordinary information bundle, which is ordinarily bigger than 1000 bytes, a little parcel has a littler likelihood of impacting different parcels on account of its shorter transmission time. Second, RTS/CTS control outlines can save the data transmission. Consequently, a fizzled bundle transmission after a fruitful RTS/CTS trade must be created by channel corruption. ARA separates the edge misfortunes through the utilization of RTS control outline. At the point when an information outline transmission comes up short, a RTS control edge will be sent at the same rate as the fizzled casing. On the off chance that the CTS control edge can be gotten, then present channel condition has a high likelihood of supporting the current transmission rate. Consequently, the loss of the past information casing is created by crash. Then again, if the RTS/CTS trade is fruitful however the accompanying information casing falls flat, then the edge misfortune must be brought about by channel blurring. Through this strategy, ARA can correctly separate the edge misfortunes brought on by both channel blurring and impact. For the second rule, ARA utilizes a quick yet exact rate alteration instrument. As clarified above, if the RTS/CTS trade is fruitful yet the following information casing still falls flat, the disappointment is brought on by channel blurring. In this way, the information rate will be diminished because of such environment changes. On the off chance that the edge misfortune is brought on by crash, the transmission rate will stay unaltered. The rate change in ARA is quick yet exact given the condition that ARA can definitely focus the reason for casing misfortunes. The greater part of the current rate adjustment calculations utilize sequential achievement check or successive disappointment consider their metric to alter the information rate. In any case, this system is incorrect, as well as loses the chance to get the short addition time of solid sign. ARA utilizes RTS and the accompanying information casing to distinguish channel blurring and in this manner have the capacity to decline the transmission rate rapidly and unequivocally. ARA likewise utilizes the achievement tally to expand the information rate however it doesn't essentially need to be continuous. As expressed beforehand, the likelihood of a fruitful transmission after ten sequential achievement transmission is just 28.5%. By fulfilling the greater part of the rules showed in the above area, a proficient and reasonable rate adjustment calculation is proposed. Figure 6 demonstrates the state move graph for ARA.

#### C. Implementation

ARA is actualized on Madwifi, which is an open source IEEE 802.11 gadget driver for Atheros cards in Linux and Freebsd. In this variant, ARA characterizes two limit parameters named (Ts = 8) and (Pth = 1), Ts is the edge used to expand the transmission rate. Pth is the edge used to start the RTS/CTS trade. In the event that an information transmission falls flat, ARA will enter a state where RTS/CTS trade strikes help separate the reason for this casing misfortune. It likewise holds two rate file sets, specifically rix and cix. rix is utilized to situated the

current information transmission rate list and cix is utilized to set the current RTS transmission rate file. A rate list relates to the genuine transmission rate, for instance, in IEEE 802.11g, there are altogether 12 diverse transmission rates. Going from 1 Mbps to

Figure 6. ARA Algorithm

54 Mbps and the rate file ranges from 0 to 11, separately. Toward the start of the state move, ARA sets the introductory rate to be the most extreme rate. It likewise instates variables m, n, and status. m is utilized to hold the quantity of casings being effectively conveyed at current transmission rate and n is the disappointment check. It must be brought up that despite the fact that n is the disappointment include; it is NOT utilized the rate alteration metric to decline the information rate. It is just utilized as a condition test to choose whether ARA needs to start RTS/CTS trade. status holds the current status: Rts\_off and Rts\_low. After the variables have been instated, ARA will sit tight for the impending information outlines. At whatever point an information edge is found in the transmission line, ARA will attempt to send the information without the assistance of RTS. On the off chance that the information is conveyed effectively, ARA will build m by 1 and reset n to 0. It will likewise reset status to Rts off on the grounds that next edge will be transmitted without the assistance of RTS/CTS. At the point when m achieves the limit Ts and current transmission rate is not greatest rate, the rate will be expanded. In any case, if a transmission falls flat, ARA

will build n by 1. Note that right now, m is not reset on the grounds that whether outline disappointment is in fact brought on by channel corruption or not will be not known. At the point when n is equivalents to 1, it implies the past information transmission has fizzled. ARA will attempt to separate the reason for this disappointment. It will first send a RTS at the same rate as the fizzled information outline (cix = rix), indicated as Rtshtx. On the off chance that the comparing CTS can be gotten, a few things can be affirmed. In the first place, the channel condition may help the current transmission rate since RTS is transmitted at the same rate as the fizzled casing. Second, there is a high likelihood that the past casing misfortune is brought on by crash. Third, the transmission capacity has been held as a result of the fruitful trade of RTS/CTS. Since the reason for the past information outline misfortune is impact, it is not expected to change the transmission rate record rix. Achievement tally m will be continued on the grounds that the channel condition has not change. It must be called attention to that the length of the channel condition does not change, m ought not be changed. This is truly not quite the same as other rate adjustment plans and is one of the reasons why ARA is more proficient. Notwithstanding, it is still conceivable that the Rtshtx fizzled, this happens when the channel condition debases. Since RTS has a little size and has a low likelihood to impact, there is a high likelihood that the disappointment is created by channel blurring. To affirm this, ARA will send the RTS at the most reduced rate (cix = 0), indicated as Rtsltx, furthermore status will be set as Rts low

As of right now, it has a high likelihood that Rtsltx will be transmitted effectively in light of the little size and powerful transmission rate. After the relating CTS has been gotten, the transfer speed has been saved for the following information parcel. Review that the information rate list rix is still not changed in the above steps. Thusly the information will in any case be transmitted utilizing the first rate. It is likely that this casing won't be conveyed effectively. Since the reason for this disappointment is unmistakably because of channel blurring, the transmission rate will be diminished and each variable is reset. ARA falls again to introductory state and the entire procedure rehashes.

#### D. Evaluation

#### • Static Station in a Collision Free Network

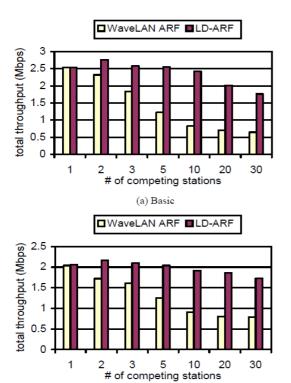

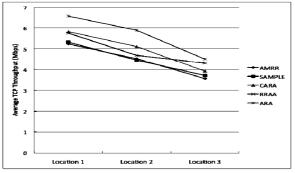

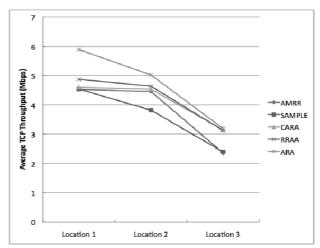

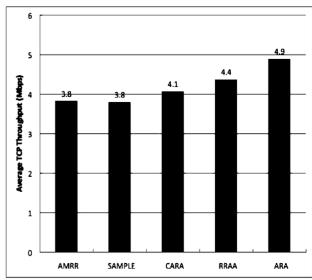

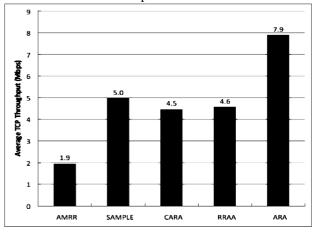

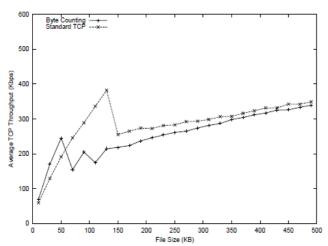

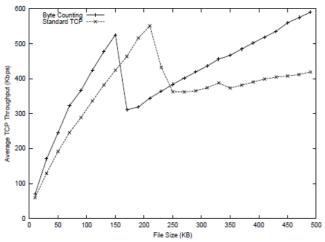

Figure 7. TCP Throughput for a Static Station in a Collision Free Network

#### • Static Station in a Collision Dominated Network

Figure 8. TCP Throughput for a Static Station in a Collision Dominated Network

#### Mobile Station in a Collision Free Network

Figure 9. TCP throughput for a Mobile Station in a Collision Free Network

#### Static Station in Campus network

Figure  $\,$  10. TCP Throughput for a Static Station in Campus Network

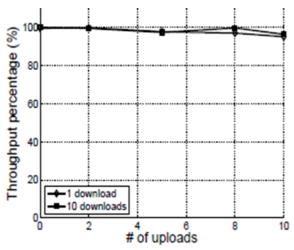

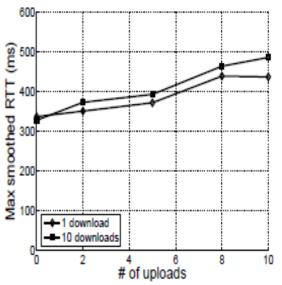

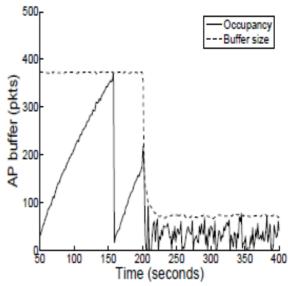

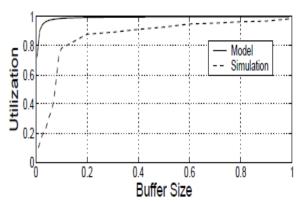

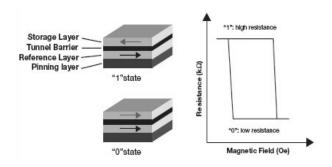

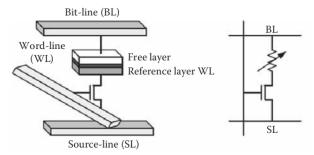

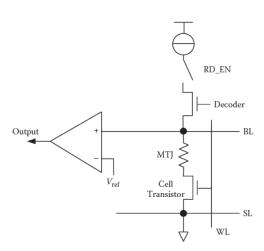

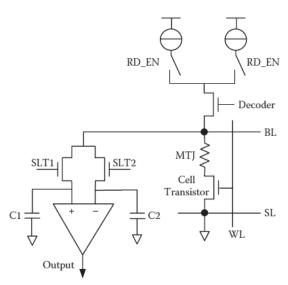

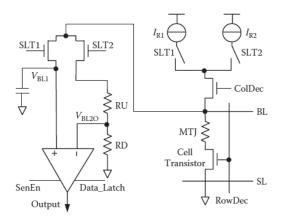

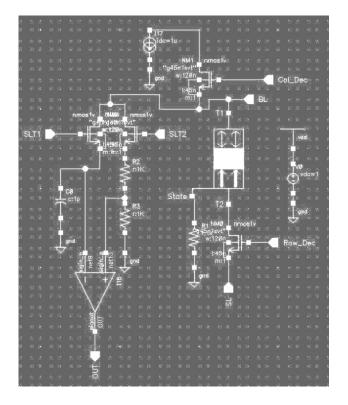

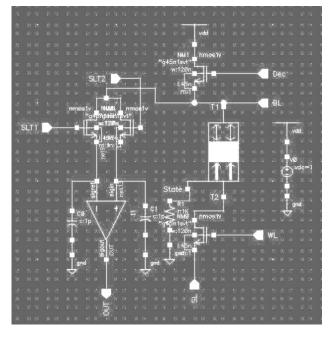

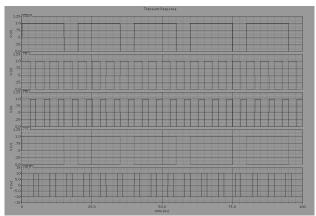

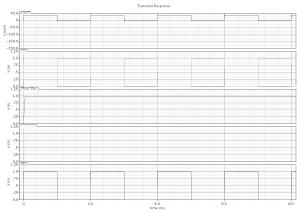

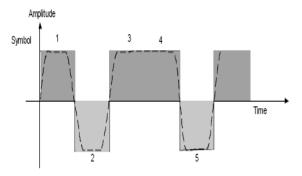

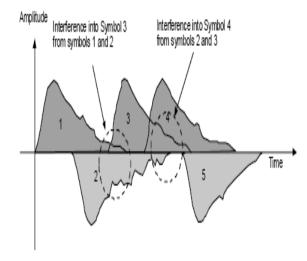

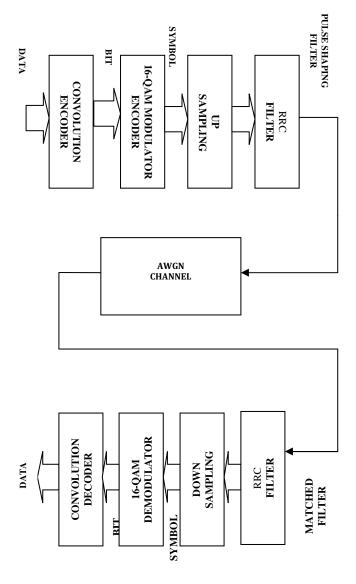

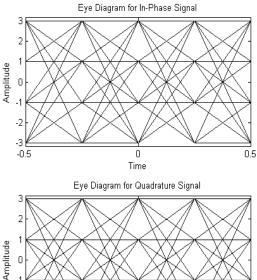

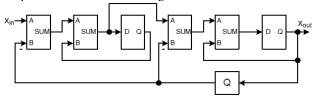

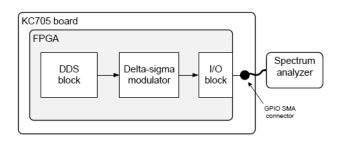

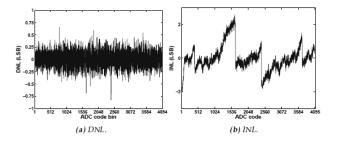

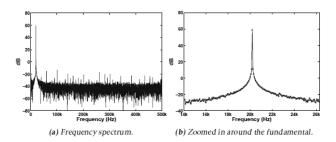

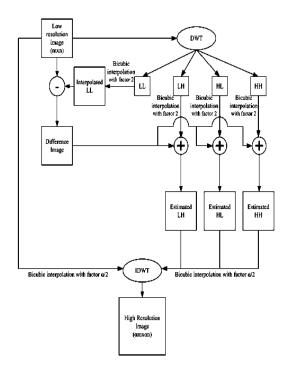

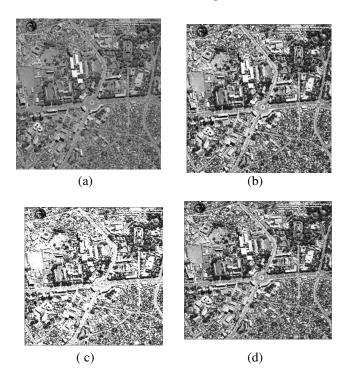

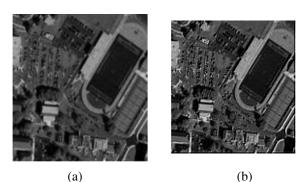

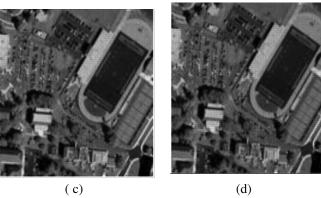

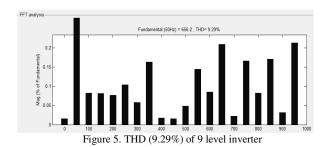

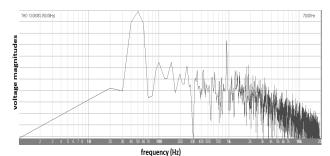

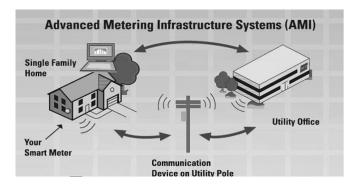

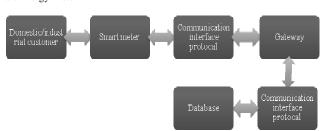

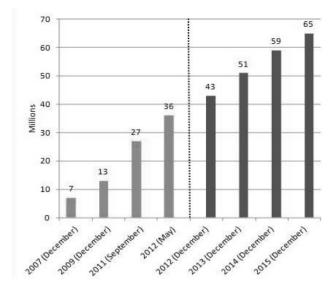

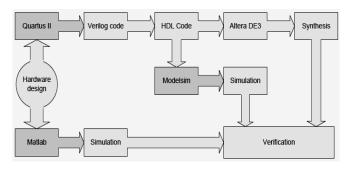

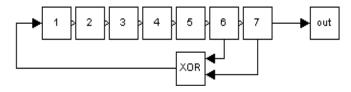

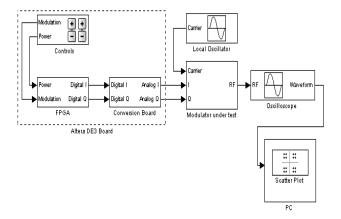

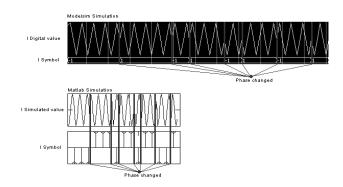

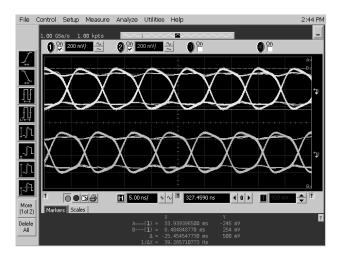

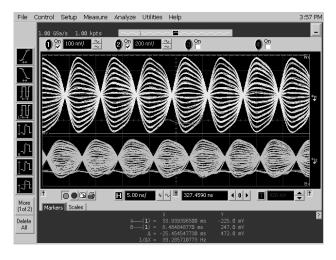

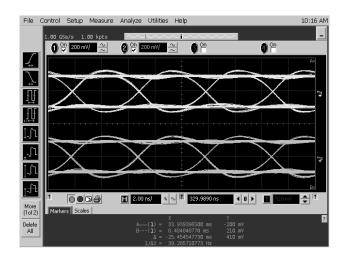

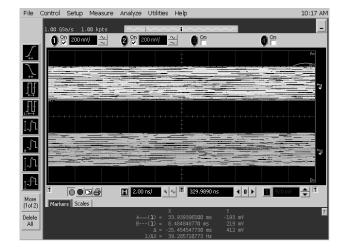

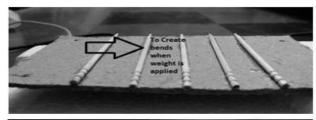

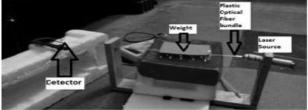

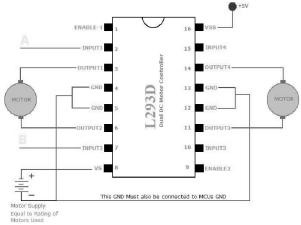

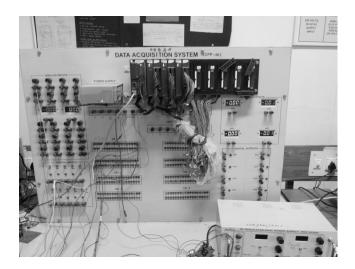

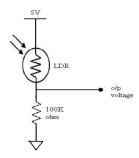

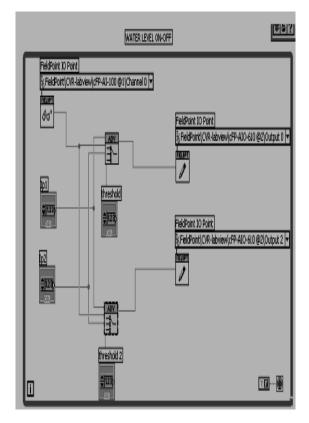

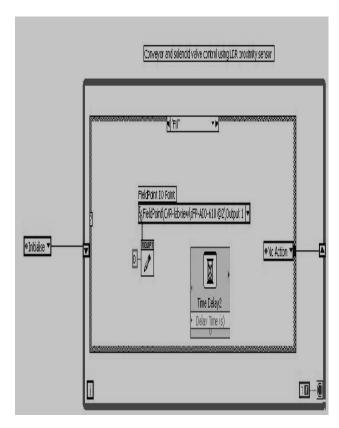

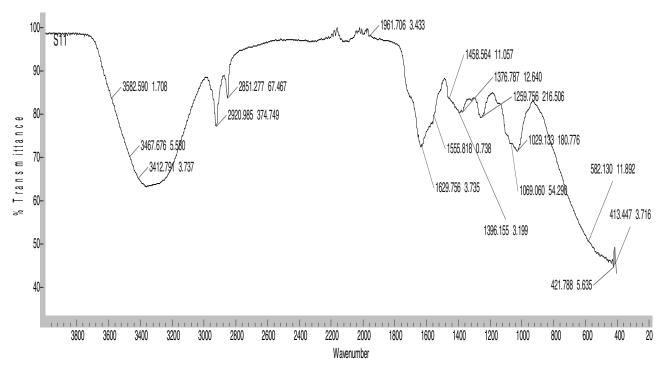

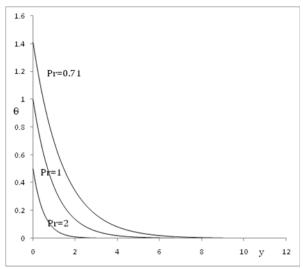

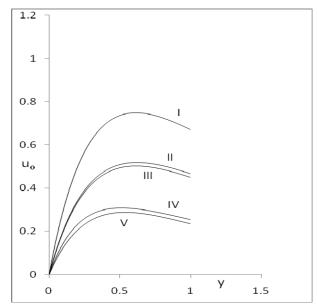

#### IV. VARA DESIGN