# CVR JOURNAL OF SCIENCE & TECHNOLOGY

### CVR COLLEGE OF ENGINEERING

(An Autonomous College affiliated to JNTU Hyderabad)

Mangalpalli (V), Ibrahimpatnam (M),

R.R. District, Telangana. – 501510

http://cvr.ac.in

**EDITORIAL**

Volume 6 of the biannual journal of our college, CVR Journal of Science and

Technology, is being brought out with 18 papers selected out of several papers received

from the different branches of Engineering and Science.

Apart from the staff members of our college, the authors include a few from external

institutions. It is gratifying to note the serious pursuit of research by our staff members. I am

confident that the research activity will help in contributing to the quality of teaching apart

from helping in providing valuable guidance to students in technical topics of current

interest.

It is my earnest hope that the interest in contributing technical papers of high quality to

our journal will grow further among the staff members of all the departments.

I wish to thank all the members of the Editorial Board for their support. Special

thanks are due to Sri Deepak, Programmer in the Department of CSE for formatting the

papers in camera ready form and for making the journal ready for final printing.

K.V. Chalapati Rao

Editor

### **CONTENTS**

| ISSN | 2277 | -391 | 16 |

|------|------|------|----|

|      |      |      |    |

CVR Journal of Science and Technology, Volume 6, June 2014

| Object Tracking Using Computer Vision Techniques.  N. Sushmitha, B. Meena, Mr.K.V Sriharsha, Dr N.V Rao                                                                            | 1   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Managing semantics of graphic components through remodeling traditional display files.<br>Dr. Hari Ramakrishna                                                                     | 7   |

| Big Data Mining: Problems and Prospects.  Nayani Sateesh                                                                                                                           | 13  |

| Design And Implementation Of A Cyclic ADC For CMOS Image Sensors  O. Venkata Krishna, B. Janardhana Rao                                                                            | 17  |

| Stochastic Modeling and Availability Evaluation of Computer Systems  Wg Cdr Varghese Thattil and Swetha Akula                                                                      | 25  |

| Design of On-Chip Testing Memory for High Speed Circuits  M.V. Sushumna                                                                                                            | 31  |

| Implementation of Wireless Remote Control for Bore-well Motor.  Shakeel Ahmed and N.Nitin Kumar                                                                                    | 39  |

| Improving the Bit Error Rate of OFDM using Convolutional codes<br>R.Prakash Kumar                                                                                                  | 44  |

| Implementation of Digital Filters for the Removal of Artifacts from Electrocardiogram <i>P. Naga Malleswari</i>                                                                    | 48  |

| Simplified LS and Modified MMSE Estimators for Channel Estimation of OFDM B. Janardhana Rao and O. Venkata Krishna                                                                 | 58  |

| Design Of High Performance Configurable Radix-4 Booth Multiplier Using Cadence Tools Dr.T. Esther Rani                                                                             | 66  |

| Design of Low Cost Sigma-Delta Analog-to-Digital Converter for Audio Applications  Athira G. Krishna                                                                               | 75  |

| Comparison of Adaptive Filtering Algorithms Based on Time Varying Weighting Factor<br>Mohammed Abdul Nasar                                                                         | 81  |

| Design and implementation of High Performance Voltage-Controlled Oscillator using CMOS Technology G. Venkateswarlu                                                                 | 87  |

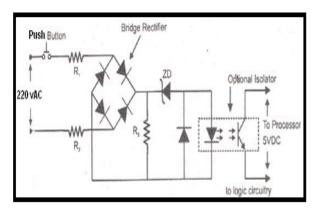

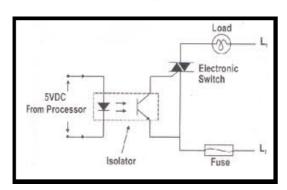

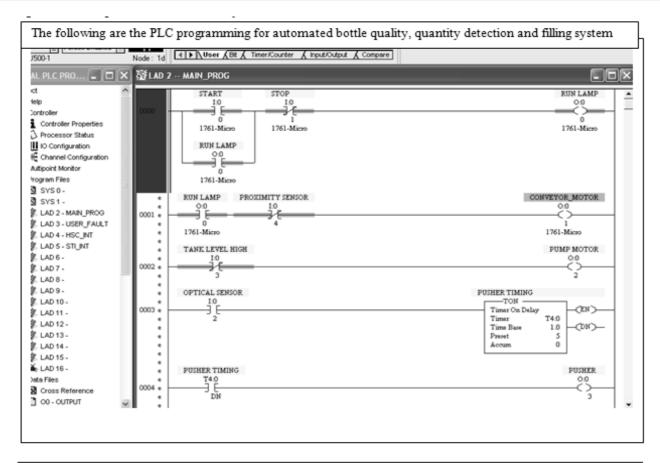

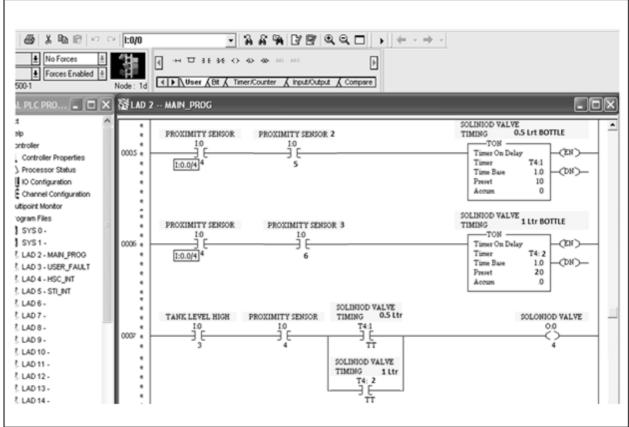

| SCADA Based Automated Bottle Quality & Quantity Detection and Filling System by Using PLC Mr.P.Choudesh Varma and Mr.G.Venkateswarlu                                               | 93  |

| Paratransit Operations in Roorkee S. Praveen                                                                                                                                       | 102 |

| Synthesis characterization and spectral studies of bisdithiocarbamate of urea and its Metal complexes <i>P.Saritha</i>                                                             | 108 |

| An Empirical study of the Citizen's Perception of Automation Process of Government in India through E-Governance Dr. M.S.Bhat, Dr. Piyush Gupta and Maj.Gen. (retd.) Dr. R.K.Bagga | 112 |

## Object Tracking Using Computer Vision Techniques

N. Sushmitha<sup>1</sup>, B. Meena<sup>2</sup>, Mr.K.V Sriharsha<sup>3</sup>, Dr N.V Rao<sup>4</sup>

<sup>1</sup>CVR College of Engg /CSE Dept, Hyderabad, India

Email:sushuma.shiri@gmail.com

<sup>2</sup>CVR College of Engg /CSE Dept, Hyderabad, India

Email:meenareddy38@gmail.com

<sup>3</sup>CVR College of Engg /I.T Dept, Hyderabad, India

Email: sriharsha.phd@gmail.com

<sup>4</sup>CVR College of Engg /CSE Dept, Hyderabad, India

Email:nvr@ieee.org

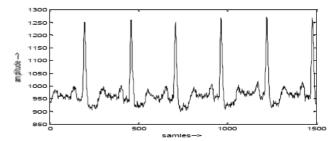

Abstract--Computer vision basically deals with different factors such as modeling of camera, lighting, color, texture, shape and motion that affect images and videos from visual inputs. Object detection and tracking are important components in many computer vision applications including activity recognition, traffic monitoring and automotive safety. This paper is about locating a moving object (or multiple objects) over a time using a stationary camera and associating the target object detections in consecutive video frames. In this perspective a video is captured by digital camera and is used for motion analysis. In the first stage of experiment frame differencing algorithm is chosen for object detection and its motion is estimated by associating the centroid of the moving object in each differenced frame. In the second stage of experiment same algorithm is chosen for object detection but motion of each, track is estimated by Kalman filter. However the best estimate is made by combining the knowledge of prediction and correction mechanisms that were incorporated as part of Kalman filter design. The tracking results obtained from two stages of experiment are presented for discussion.

Index Terms- computer vision, object tracking, centroid, image filtering, grey thresholding, morphological, dilation, erosion, trajectory, point tracking, Kalman filter, dynamic model, observation model

### I. INTRODUCTION

Earlier computer vision systems [1] are only concern with scene analysis. The scene analysis is about recognizing the activities in a scene and to assimilate information from the sequence of images as a whole. There are two types of scene analysis one is static and the other is dynamic. Static scene analysis is about

recognizing and understanding the activities of static objects from a stationary camera. There is a little scope of applying static scene analysis in the current day applications. Nowadays while observing a scene, the activities will never be static, they will be changing or moving rapidly with in a fraction of seconds. In such case there is a necessity to perform dynamic scene analysis. The changes in the scene may arise due to motion of camera or object. However system must be able to detect and track the changes that are going on rapidly over stationary or non stationary background. The dynamic scene analysis can be done in three cases stationary camera among moving objects (SCMO), Moving camera among stationary objects (MCSO), moving camera among moving objects (MCMO). As the researcher goal is to identify the objects of interest, track the motion, compute the characteristics of motion, SCMO gained much attention in this regard. In our paper the discussion is confined to stationary camera among moving objects. The analysis is about interpreting the activity of the scene by indentifying the objects of interest, classifying them and estimate the trajectory of object in the image plane as it moves around the scene. For tracking an object over a scene it is essential to represent [2] an object either using a shape or appearance. There are different ways in which an object can be represented by shape; one way is representing an object by a point (centroid), or a set of points. The other representations are primitive geometric shapes such as rectangle, ellipse are used for tracking rigid and non rigid objects. There are also other categories of representations like boundary of an object (contour) and region inside the object (Silhouette) which are used for tracking complex non rigid shapes. As point representations are much more suitable for

tracking objects that occupy small regions in a space, they are used for dynamic scene analysis in our experiment. Appearance based representation is also enormously used in many computer vision applications especially for tracking objects accurately in a scene. Template is one among which is formed using geometric shapes or silhouettes. The well and extensively used template matching for tracking objects in successive fames uses template representation. This approach works well for the cases where position and orientation simply called as pose; do not vary while tracking the objects in successive frames .The other is probability density based. These may be parametric or non parametric. Parametric take 1D Gaussian distribution, n-D Gaussian distribution or Gaussain Mixture Models (GMM). The objective parametric probabilities density based representation is to characterize an image region by its statistics. If the statistics differ from background, tracking should be enabled. Coming to Non parametric representations the most widely used for target representation is color histogram, which is mathematical equivalent to discrete probability density function of target region.

### II. OBJECT DETECTION

Whenever objects appear in a video for tracking, they require object detection mechanism. It is the first step for dynamic scene analysis. It includes image segmentation process where foreground objects are separated from background objects by applying thresholding techniques. There is a possibility that foreground pixels may be affected with noise where image filtering is required for noise removal. The moment filtered foreground pixels are obtained; they are grouped into connected regions. The connected regions are further used to extract individual object features such as bounding box, area, perimeter etc.

### III. DIFFERENT TYPES OF OBJECT DETECTION MECHANISMS

Object detection [3] can be achieved by using a representation of a scene called background model and the comparing the model with each incoming frame. Any significant change observed in the image from the background model is considered as moving object and is

processed further for analysis. This method is known as background subtraction .It is a popular pre processing step used in computer vision applications as it allows detections of objects of interest in stationary and non stationary background even when the camera is fixed. However the subtraction results in large number of false detections with the changes in illumination and fine scale motion in the scene. There are also statistical based detection methods like adaptive background mixture modeled by mixture of Gaussians. In order to know whether a pixel belong to foreground or background, Gaussian distribution of mixture model for that pixel is evaluated . The most simple one is temporal differencing (or frame differencing) takes pixel wise difference between two or more consecutive difference. This method is unable to detect the foreground object when texture is non uniform and when its speed is changing. However in our experiment We have chosen this method in order to avoid false detections.

### IV. FIRST STAGE OF EXPERIMENT

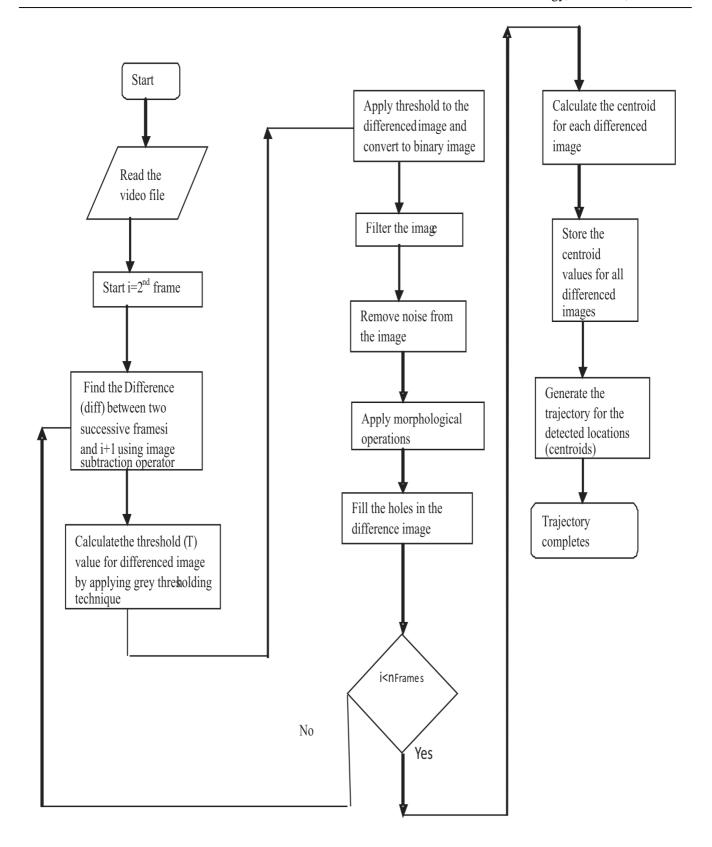

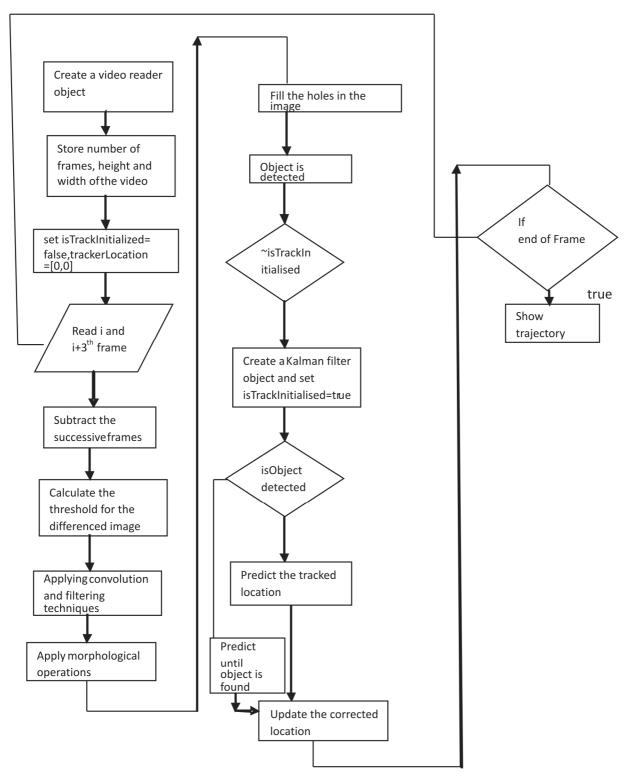

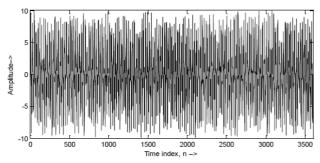

A. Algorithm for object detection and tracking

In the first stage of experiment in order to identify the moving object in successive frames, frame differencing technique is applied. In this technique [4] a current frame is always subtracted from the previous frame by using image subtraction operator. The resulting differenced image is transformed to binary image as and when grey thresholding is applied. For removal of blur [5] (considered as Gaussian noise) in differenced image due to linear motion or unfocussed optics, filtering operation is applied. As it is known that Wiener filter is suitable for reconstruction of original from the noisy image and hence it is chosen for image filtering operation. Finally dilation and erosion operations are applied for removal of image imperfections. For each of the moving object that is identified in the preprocessed image, the centroid is computed. This centroid represents the moving object in each of the differenced image. Finally a trajectory is drawn by connecting the centroids of all differenced images [6]. The whole process is summarized in the following flowchart

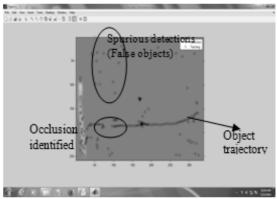

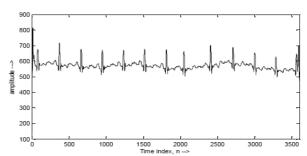

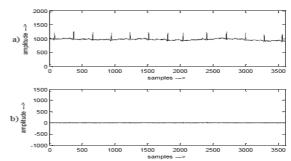

Figure 2.a: tracking results for a single object on adjacent Frames

The results obtained from fig 2.a plotted on the graph With frame number on X axis and number of objects on Y axis

Figure 2.b: graph showing moving object along with spurious detection

The algorithm is again applied on odd number of frames and results obtained as follows.

Figure. 3: Tracking results for single object over odd number of frame

### V. CLASSIFICATION OF OBJECT TRACKING

Object tracking [7] can be categorized as point tracking, kernel based and silhouette based. Point tracking require object detection in every frame whereas kernel based and silhouette tracking only requires object detection when object first appear in the scene. In our paper the discussion is confined to point tracking. In this objects that are detected in successive or odd number of frames are represented by points. With an association of centroid of moving object over successive frames which includes object position and motion. Point tracking algorithms are either deterministic or statistical. Measurements obtained from video scene may be affected with noise and also object motion may undergo random perturbations. These are the challenges that are addressed in the deterministic methods. Statistical methods remove these uncertainties while estimating the state of an object in associated detections. Kalman filter falls under this category which can be applied to stationary and non stationary environments.

#### VI SECOND STAGE OF EXPERIMENT

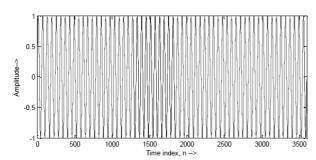

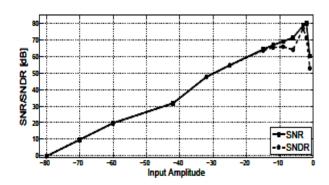

### A. Kalman filter for object tracking

Kalman filter [8] is s recursive predictive filter where each updated estimate of the state is computed from the previous estimate and the new input data. Hence only previous estimate requires storage. It eliminates the need for storing the entire past observed data. It is computationally more efficient than computing the estimate directly from the entire past observed data at each step of filtering process. In the previous case tracking results are not precise because of lack of prediction and correction mechanisms. Kalman filter make a good estimate by predicting the state of an object with dynamic model and correcting its state with observation model. Thus error covariance of the estimator is minimized by giving accurate tracking result.

### B. Algorithm for frame differencing using Kalman filter

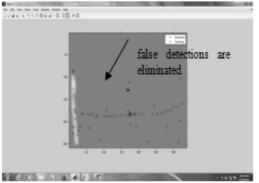

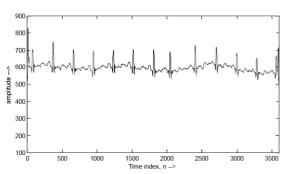

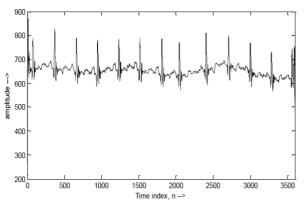

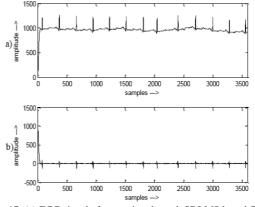

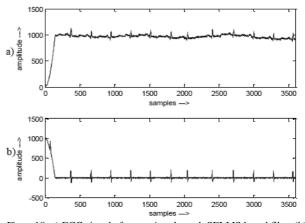

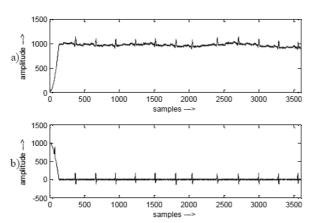

Figure.4: Object detection tracking using Kalman filter

Figure.5: object detection and tracking using Kalman filter

From the fig. 5, it is observed that accurate tracking results were obtained with implementation of prediction and correction mechanism when compared to fig. 2 & 3.

#### VII. CONCLUSION

In the first stage of experiment, moving object is detected and tracked successively by applying the algorithm on adjacent and odd number of frames. From the results obtained it is observed that comparatively less number of spurious detections were found by applying frame differencing algorithm on odd number of frames. As it was found that tracking results are not accurate in the first stage of experiment, Kalman filter is implemented and the path of the moving object is predicted and corrected.

### VIII. FUTURE WORK

In this paper the discussion is confined to tracking single objects from a stationary camera, so the work is to be extended further on tracking multiple objects. The experiment is to be continued on moving object when camera is stationary and moving and at the same time it should possess the ability to cope up with complexities such as moving and changing objects, changing illumination and changing view points.

#### IX. REFERENCES

- [1] Ramesh Jain , Rangachar Kasturi, Brian G.Schunck , Machine Viraw-Hill , Inc., ISBN 0-07-032018-7,1995

- [2] A.Yilmaz, O. Javed, and M.Shah, "object tracking: A srvey", ACM Computing Surveys, Vol. 38, No-4, Article -13, December 2006.

- [3] N Prabhakar , V . Vaithiyanathan, Akshaya Prakash Sharma , Anurag Singh and Pulkit Singhal ,"Object Tracking using Frame Differencing and Template matching", Research Journal of Applied Sciences , Engineeering and Technology 4(24):5497- 5501, December 15,2012.

- [4] Macros martin-Fernandez, Emma Mnoz-Moreno, Carlos alberola-Lopez, "A Speckle Removal Filter Based on Anisotropic Wiener Filtering and the Rice Distribution", IEEE Ultrasonics Symposim,2006.

- [5] Rasit Koker, Serap Cakar, Cemil Oz, "Moving Object detection and Target Prediction in Video Image Using Computer Vision ", proceedings of International Conference on Signal Processing, IJCI, 2003.

- [6] Himani S.Parekh ,Darshak G.Thakore ,Udesang K. Jaliya ,"A survey on Object Detection and Tracking Methods", International Journal of Innovative research in Computer and Communication Engineering ,Vol.2,Issue 2,Febrary 2014.

- [7] Ramsey Faragher, "Understanding the Basis of the Kalman Filter via a Simple and Intuitive Derivation", IEEE Signal Processing Magazine, September 2012

### Managing Semantics of Graphic Components Through Remodeling Traditional Display Files

Dr. Hari Ramakrishna, CBIT/ Computer Science and Engineering, Hyderabad, India Email: dr.hariramakrishna@rediffmail.com

Abstract—Management, reuse and customization of semantics of graphic components remodeling traditional display file models and graphic frameworks is presented. All these models are well tested in several graphic applications. A model debug driver tool application is adopted for the presentation of these models. Typical C++ code segments and Microsoft based visual studio application outputs are presented. These models are more generic and they can be used in any application domain using any language and development environment that support basic graphic primitives. The traditional ways of handling display files are also presented.

Index Terms—Display files, Semantic graphic behavior, graphic components, graphic frameworks, debug driver tool, Microsoft graphic applications, object oriented models and frameworks. Dynamic display files.

### I. INTRODUCTION

Software industry is looking for rapid application development mechanisms with client orientation and short time span delivery, increasing quality and withstanding rapid changes in technology and requirements.

In this connection exporting third party tools plays a major role. Using third party tools decreases testing time. Development of frameworks for increasing degree of reuse has become an important focus. Customization of such frameworks as per client requirements increases importance of frameworks. Frameworks are different from libraries; client code is embedded in frameworks whereas client code includes and calls libraries. [1]

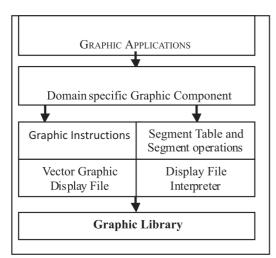

Display file concepts are traditionally used in several graphic models. Geometry of a graphic system is stored as a set of graphic instructions in display file. Display file interpreter recognizes these commands and generates graphics as per the client requirements.

Present day graphic and CAD systems are used at advanced levels. Present graphic systems demand implementation, and simulation of graphic components such that they mimic original real time components. Such requirements demand managing semantics of

graphic components. These components should be in a position to implement their behavior, communicate with other components of the system and generate required graphics dynamically. These requirements demand remodeling of traditionally used graphic display file concepts.

### II. TRADITIONAL DISPLAY FILE CONCEPTS

Display files store graphic behavior of elements of any graphic or GIS systems in a specific defined structure. The display file for general purpose interactive graphics software is divided into a set of segments such that each segment corresponds to a component of the overall display file. For example, in a building graphics information system, each civil engineering building element is treated as a segment. In other words, windows, doors, racks etc, which are known as civil engineering building elements, are stored in the display file as graphics segment. Sets of attributes are associated with each segment. All these attributes of segments are stored in segment-table.

The information that must be associated with each segment and how the information might be organized are important in understanding display file concepts. Each segment has its own unique name, and it can be referred with that name. For performing some segment operations like changing the visibility of segment, distinguishing the segment from other segments is required. When referring to a display file segment, set of display file instructions that belong to that segment are required. This may be determined by knowing where the display file instructions for that segment begin, and how many of them are there in its specific display file. For each segment, we need some way of associating its display file position information and its attribute information with its name. Sample display file attributes are listed in table 1.

Segmentation can be managed through a set of procedures to create, open, close and transform a segment. Sample user-routines needed to manage segments are listed in table 2.

The object-oriented dynamic display file models presented in this paper do not need implementation of segmentation requirements. The objects take care of segmentation requirements as each graphic segment is defined as an object.

### III. DISPLAY STRUCTURE MODELS

In the structure of the traditional display file, each display file command contains two parts: operation code (opcode), and operands. Opcode indicates what kind of command it is. Operands refer to required coordinates and other arguments required for executing the opcode. The display file is made up of a series of these instructions. The Display file stores all this information forming a huge storage. In the new concepts, this problem is solved as the display file for each component is generated dynamically. Only domain specific component state, and behavior identity are stored in the object itself. This information is helpful in the generation of display file content required for rendering that object.

In the traditional model, the display file must be large enough to hold all the commands needed to create the image. One must assign meaning to the possible operation code before proceeding to interpret them. For example, in a building graphical information system, various geometrical elements such as point, line, circle, arc and polygon may be considered. The general attributes of any simple display file instruction are -the type of the geometrical element and its color, required coordinates and other geomantic information specific to that element.

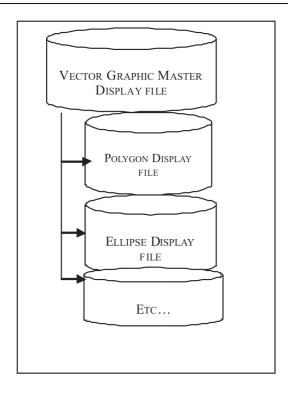

The instruction is interpreted by invoking the required vector generator. The vector generators of special geometrical elements may need more information than that available in the main display file. This information is also in the form of graphics commands, which are stored in a separate display file. For example, all the instructions for plotting a polygon are in the polygon display file. Each vector generator of this type has its own interpreter for the interpretation of these commands. The starting-address and size of these instructions also are the needed attributes which are stored in the main display file. Figure 1 shows model sample storage of this type.

The information of the display file is useful to model the object and create the required image. The reason behind this is two-fold: some measure of device-independence is achieved, and it is easy to perform image transformation by changing the position and orientation of the required image. The display file contains the information necessary to construct the required image. The information can be in the form of instructions such as "move the pen", "draw a line", and "plot the required polygon".

Saving instructions such as these usually takes much less storage than saving the picture itself. Each instruction indicates an action for the display device. A display file interpreter is used to convert these

instructions into actual images. The display file interpreter serves as an interface between graphics program and the display device. The display file instruction may be actually stored in a file either for a display layer or for transfer to another machine. Such files of imaging instruction are sometimes called "metafiles". Table 3 presents sample vector-generating algorithms.

The vector generation algorithms used for dynamic display file based graphic framework presented are supported as a set of function libraries developed using Microsoft MFC classes. These algorithms are portable to any development environment that supports basic graphic primitives.

These functions are used by the display file interpreter while converting the display file instructions into the required picture on the display device. This process of generating image makes our graphics software independent of the nature of the display device and upon its software.

Whatever may be the way of storing and plotting the required images we require some tools for interaction with the graphics system. Table 4 presents various sample user-routines for building-graphics information system. Figures 1 and 2 present display file models for graphic framework. [2-6]

### III. DYNAMIC DISPLAY FILE CONCEPTS

Dynamic display files are modeled to enable computation of graphic geometry online as per the behavior of the components. Such models enable graphic components to mimic real time components.

For example a printed circuit board ( PCB ) contains several electrical and electronic components. Each component has its own behavior. Similar components repeat several times in the same PCB but with different name, location and connections. They are exhibiting behavior as per the connected components.

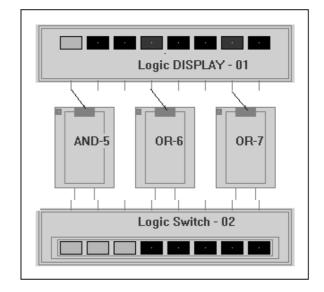

Consider simulation of a logic circuit with electronic lids and electronic switches on a PCB. The lids get on and off as per the state of switches and logic circuit output. The dynamic display files enable the geometry of such components to get computed dynamically for each event of the model.

The display file in this model will be filled with display file instructions dynamically. Same display file can be reused for several components decreasing the object and class number in an application. This will enable complex applications to run on light weight systems with low configuration.

The debug driver tool is an application used for testing faulty components of a PCB board. As per the board structure the geometry is automatically computed. The required information is name of the board, board

type and structure of components on the board and their relations.

IV. GRPHIC APPLICATION USING DYNAMIC DISPLAY FILES

Implementation of graphic frameworks and applications using dynamic display files has several layers. Sample code segments and output screens along with advantages of such models are presented.

As a first step, display file and graphic primitive generation function libraries shown in table 2,3,4 need to be implemented. Function class frameworks are used for reuse and exporting such libraries as third party tools [1].

Graphic frameworks along with some graphic foundation classes are required in the next phase. Client component definition library and graphical user interface are required to build graphic applications.

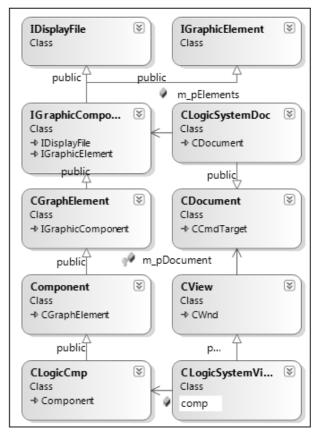

Figure 3 presents a class diagram of the application developed in Visual studio Net 2010 that uses graphic framework developed using dynamic display file concepts. These concepts are more generic and they can be implemented in any application which supports basic graphic primitives. The class diagram presents MFC document view architecture used for providing GUI for the application. CView, CDocument, CDialog etc are MFC classes. Other classes are graphic framework classes that implement dynamic display file model.

### V. CLIENT PROCEDURES FOR CONFIGURING GRAPHIC COMPONENTS

Some of the code segments that explain the implementation of dynamic display file are presented in this section. The domain client defines the component semantics for the generation of display file that compute the geometry required for display. Table 7 presents a sample code for component definition.

This procedure is not a member of CLogicCom class. It is a library function of a logic system for defining logic components. It is invoked from CLogicCom class Design method. This Design method is virtual function invoked whenever there is a need to re-compute the geometry of a component as per its behavior and status in the system. For example, in the LID device display the lights become on or off as per the data available in the system. The display file instructions are generated dynamically through invoking the procedure listed in table 9.

Figure 4 presents Logic Switch and Logic Display as per the user interface and logic circuit output. The green and white represent 1 and 0 (on and off). The red and black represent error and invalid data. The positions 4 and 7 represent error in red as the pins 4 and 8 are carrying invalid data. The first display is shown in green as the gate is AND gate and switches 2 and 3 are representing one. Depending on connections the

component changes geometric behavior as per the requirement of simulation like components.

#### **CONCLUSIONS**

The traditional display file models and a model graphic framework based on traditional display files are presented. The dynamic display file concept and class diagrams along with sample code segments to demonstrate dynamic display file functioning concepts are presented. Output of a graphic application using dynamic display file concepts is presented. These concepts are applicable to any similar applications irrespective of application domain, object oriented development environment and development language with basic graphic support. The relation subsystem and other inherent concepts used are not covered in this paper.

#### REFERENCES

- Dr.Hari Ramakrishna, "A pattern language and traditional programming practices for exporting functionality" CVR Journal of Science & Technology, released in December 2013 ISSN 2277-3916

- [2] Dr.Hari Ramakrishna, "Pattern Approach to Build Traditional Graphic Frame works", International 1 Journal of Computer Applications Volume 59– No.15, p35-42, December 2012. Published by Foundation of Computer Science ISSN: (0975 – 8887), New York, USA

- [3] Dr. Hari Ramakrishna, "Design Pattern for Graphic/CAD Frameworks", Ph.D thesis submitted to Faculty of Engineering Osmania University March 2003,

- [4] Christopher Alexander, "An Introduction for Objectoriented Design", A lecture Note at Alexander Personal web site www.patternlanguage.com

- [5] Pattern Languages of Program Design. Edited by James O. Coplien and Douglas C. Schmidt. Addison-Wesley, 1995

- [6] Erich Gamma, Richard Helm, Ralph Johnson, and John Vlissides, "Design Patterns: Elements of Reusable Software Architecture", Addison-Wesley, 1995

- [7] Hari RamaKrishna "COM Applications for Real time Electrical Engineering Applications" IEEE sponsored International Conference at Bangalore - 2000.

- [8] Hari RamaKrishna "Generation of flooring and wallpaper patterns using computer graphics" Proceedings of the First National Conference on Computer Aided Structural Analysis and Design, Jan 3-5,1996, Engineering Staff College of India and University College of Engineering, Osmania University, Hyderabad.

- [9] Newman, W. S and Sproul, R.S (1981), Principles of interactive computer graphics McGraw-Hill International, second edition.

### TABLE I SEGMENT TABLE ATTRIBUTES

- (1) Segment name

- (2) Segment's starting address of the display file

- (3) Segment size i.e. number of instruction of segment

- (4) Segment visibility i.e. on or off

- Segment transformation parameters i.e. scaling, translation, rotation around x,y,z axes

- (6) Segment reference point that is useful for transformations

- (7) Segment transparency (on or off) useful for hidden line and surface elimination Etc.

### TABLE II GRAPHIC SEGMENT TABLE INSTRUCTIONS

- (1) Create-segment (n)

- (2) close-segment (n)

- (3) Append-segment (n)

- (4) set-segment-visibility (n,I)

- (5) Rotate-segment (n,ax,ay,az)

- (6) translate-segment(n,tx,ty,tz)

- (7) Set-segment-reference-point (n,x,y,z)

- (8) scale-segment(n,sx,sy,sz)

- (9) Show-segment (n)

- (10) delete-segment (n)

### TABLE III DISPLAY ALGORITHMS

do-line3d (lc,bc,z,y,z), do-point3d(lc,x,y,z), do-circle3d(lc, cx,cy,cz,r,ax,ay,az), doarc3d(lc,cx,cy,cz,r,sa,ea,ax,ay,az), do-spehere)lc,cx,cy,cz,r) and do-poly(lc,sadd,size:

where lc is the line foreground color, cz,cy,cz are the coordinates, sa, ea are the starting and the ending angles, ax, ay, az are the angles of inclination along x,y, and z axes respectively, and r is the radius.

#### TABLE IV SAMPLE TRADITIONAL DISPLAY FILE USER ROUTINES FOR MANAGING GRAPHS

```

Move3d (x, y, z)

Line3d(x,y,z)

Line3d(lc,x,y,z)

Point3d(lc,x,y,z)

Arc3d(lc,x,y,z,r,sa,ea,ax,ay,az)

Circle3d(lc,x,y,z,r,ax,ay,az)

```

#### TABLE V SAMPLE COMPONENT CLASS

### TABLE VI SAMPLE DISPLAY FILE INSTRUCTION ALGORITHM

### TABLE VII CLASSES OF DYNAMIC DISPLAY FILE FRAMEWORK

- CDocument, CView, CLogicSystemView , CLogicsystemDoc are Microsoft based classes in Document view architecture.

- 2) CLogicCmp is inherited from Component and defines the behavior of domain specific components. In the above application components of a Degug driver tools which are defined. The function in table 6 will be invoked from design method of this class for loading behavior of a electronic LID component.

- The Component class implement all the Display file procedures as per the definition of IDisplayFile Interface and other implicit procedures required.

- The Graphic Element class implements all the procedures required for implementation of a graphic framework.

- 5) IGraphic Component is used to address all the graphic elements from Microsoft Document class. This can implement a generic persistence system which can be used to any graphic domain application using this framework.

- 6) The view class is inherited from Clogic Component for the purpose of creating a logic component. Even the GUI design can be reused for any domain similar to that of debugger driver tool.

### TABLE VIII COMPONENT CLASS MODEL

### TABLE IX COMPONENT SEMANTIC DEFINITION FOR A ELECTRONIC DISPLAY LID COMPONENT

```

void VRLogicLID(Component* ge)

{// Component color

ge->SetLineColor(ge->GetBkColor());

ge->RectSolidAt(0,0,100,100);

// Inside Area

ge->SetLineColor(LIGHTGRAY1);

ge->RectSolidAt(0,0,96,96):

ge->SetLineColor(DARKGRAY1);

ge->RectAt(0,0,94,94);

ge->RectAt(0,0,96,96);

ge->SetLineColor(DARKGRAY1);

ge->RectAt(12,0,24,85);

ge->RectAt(12,0,18,80);

// Designing light on/off status

int k=1:

for (int i=-35;i<=35;i+=10)

if (ge->GetData(k)==1)

ge->SetLineColor(RGB(0,255,0));

else if (ge->GetData(k)==0)

ge->SetLineColor(RGB(255,255,255));

else if (ge->GetData(k)==2)

ge->SetLineColor(RGB(255,0,0));

ge->SetLineColor(RGB(0,0,0));

// 255,255,255 is white(0 or OFF)

// all zeros black (junk data)

// 255 .0.0 is red(error in output)

//0,255,0 is green(1 or ON)

ge->RectSolidAt(12,i,15,8);

ge->SetLineColor(RGB(0,0,0));

ge->RectAt(12,i,-15,8);

k=k+1:

ge->SetLineColor(DARKGRAY1);

for(int i= -35; i<= 35; i+=10)

ge->MoveTo(-45,i);

ge->LineRel(-15,0);

}// displaying pins of the component

// displaying text of the components

ge->TextBkColor(LIGHTGRAY1);

ge->TextColor(RGB(255,0,0));

ge->TextAt(-40,25);

ge->Text11At(-40,-25);

} // end of the procedure

```

#### TABLE X DESIGN PROCEDURE

### TABLE XI INTERFACE IDISPLAYFILEINSTRUCTIONS

```

class IDisplayFileInstructions

public:

// Display File Functions

void virtual MoveTo(int x,int y) = 0; // 1

void virtual LineTo(int x,int y) = 0; // 2

void virtual TextAt(int x,int y) = 0; //3 horizontal

void virtual MoveRel(int x,int y) = 0; // logical 1

void virtual LineRel(int x,int y) = 0; // logical 2

void virtual TextRel(int x,int y) = 0; // logical 3

void virtual VerticalTextAt(int x,int y) = 0; // 4 Vertical

void virtual VerticalTextRel(int x,int y) = 0; // logical 4

// 5 Rectangle

void virtual RectAt(int x,int y,int a,int b) = 0;

// 6 used even for circles ellipses

void virtual ArcAt(int x,int y,int sa,int ea,int r1, r2) = 0;

// 7 Filled Solid Ellise

void virtual EllipseSolid(int x, y, a, b) = 0;

// 8 Solid Rectangle

void virtual RectSolidAt(int x,int y,int a,int b) = 0;

// 9 Set color of line

void virtual SetLineColor(COLORREF i) = 0;

// 10 Set FillColor

void virtual SetFillColor(COLORREF i) = 0;

void virtual Text1At(int x,int y) = 0; // 11

void virtual Text2At(int x,int y) = 0; // 12

// 13 sets Text BkColor

void virtual TextBkColor(COLORREF r) = 0;

// 14 Set TextColor

void virtual TextColor(COLORREF col) = 0;

void virtual Text11At( int x,int y) = 0; // 15 Text

void virtual Text12At( int x,int y) = 0; // 16 Text

void virtual Text21At( int x,int y) = 0; // 17 Text

void virtual Text22At( int x,int y) = 0; // 18 Text

```

### TABLE XII GRAPHIC COMPONENT INTERFACE

Figure: 3 Class diagram of a graphic application in Visual studio .NET 2010 using dynamic display files

Figure: 4 A logic circuit designed with and OR gate, AND gate and logic switch components on a PCB.

### **Big Data Mining: Problems and Prospects**

Nayani Sateesh

CVR College of Engineering/ Information Technology, Hyderabad, India Email: nayanisateesh@gmail.com

Abstract - Nowadays decision making is going towards data centric and the data is becoming crucial in understanding the user needs and behavior so as to enhance the services. As the communication is going over the internet, lots and lots of data is being generated like in social networks, blogs etc., which is to be managed and analyzed properly. Big Data is becoming more prominent nowadays in the data management and processing. Big data deals with huge amount of data which is large in size, heterogeneous in nature, complex to process. In this paper I would like to review various problems in mining the Big Data and its applications in various sectors etc.

### Index Terms—Big Data, Data Mining, KDD.

### I. INTRODUCTION

From the recent past, we are hearing the most prominent topic or area is the big data in the information and communication technology (ICT) world. Because of data centric computing in understanding the user's behavior and their trend in the usage of services, Big Data is playing a vital role to gain the competitive edge in the market and to reach and increase the global customer base. In Big Data Analysis understanding the nature, significance of data and data visualization [1, 2] is more important. "Big Data" describes data sets so large and complex they are impractical to manage with traditional software tools. It relates to data generation, data storage, data retrieval and analysis of data that is remarkable in terms of size, type, and rate in which data being generated or stored.

### II. BIG DATA: TREND AND CHARACTERISTICS

As per NESSI forum big data is defined [3] as "Big Data" is a term encompassing the use of techniques to capture, process, analyze and visualize potentially large datasets in a reasonable timeframe not accessible to standard IT technologies. By extension, the platform, tools and software used for this purpose are collectively called "Big Data technologies".

### A. Data Trend

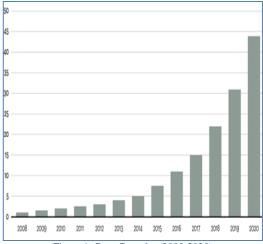

As per Oracle's review, data is being growing at 40% annual rate from the last few years and reaching by 45 ZB by 2020. The trend shows that the volume of

business data significantly grows every year which emphasis the need for analysis of the data being generated to know the insights of the data to get the competitive edge in the market to showcase their products and service in an effective way to the users and hence to stand in the top place in the competitive global market.

Figure 1: Data Growth (2008-2020) Source: Oracle 2012 (Data in Zetta Bytes)

#### A. Characteristics

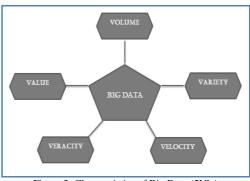

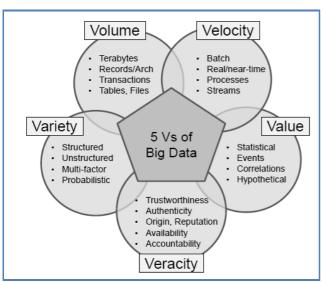

Characteristics of BIG Data can be usually called as 5 V's [4, 5]. They can be classified as Primary and Secondary characteristics based on their significance in Data Analytics.

Figure 2: Characeristics of Big Data (5V's)

Primary Characteristics – 3V's (Volume, Variety, Velocity)

Secondary Characteristics -2V's (Veracity, Value) *Volume:* It reference to the size of the data being stored. The data size can be terabytes or petabytes or even more.

*Variety:* it refers to the structure or type of the data being stored. They include unstructured, semi-structured and structured. Examples of such variety are audio, video, xml, sensor data, text files etc.

*Velocity:* it refers to data rate at which data is being generated and stored into the databases.

Veracity: It refers to trustworthiness of the data being stored

*Value:* It refers to insight of the data being extracted from the stored data is useful and which will extend the business in terms of returns and market share [6].

Figure 3: 5V's of Big Data

### III - DATA MINING vs. BIG DATA MINING

Big Data for the Enterprise: With Big Data databases, in any vertical enterprises can save money, achieve many other business objectives, grow revenue.

Using Big Data organizations can do the following:

Build new applications: Helps the organization to optimize the real data and build new applications to analyze and reuse the data

Improve effectiveness and lower the cost of existing applications: Many big data technologies are open source technology based; they can be implemented at low cost than proprietary technologies.

Realize competitive advantage: Big data can help businesses to act quickly to adapt to changes faster than their competitors.

Increase customer loyalty: Increasing the amount of data shared within the organization – and the speed with which it is updated – allows businesses and other organizations to more rapidly and accurately respond to customer demand.

### A. Data Mining

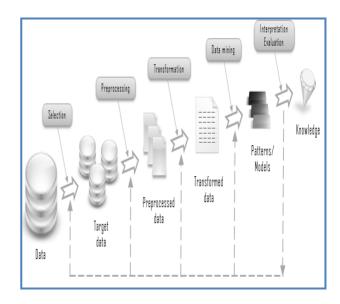

According to Simoudis (1996) - Data mining can be defined as process of extracting previously unknown,

comprehensible and actionable information from large databases and using it to make crucial business decisions. Data from various sources is integrated and then data is transformed to standard format after preprocessing. Using Data mining Algorithms interesting patterns and rules are extracted. The patterns and rules that are extracted are interpreted into the useful information which increases the knowledge of the end users.

### A. Mining Big Data – Problems

Whatever the knowledge discovery process that we discussed above is also applicable for the Big Data also. Here in this section we will look on the possible problems [4, 7, 8, 9, 10, 11] that we face during the Big Data mining process with reference to knowledge discovery process.

- a. Data integration: Since we are integrating the data from various sources, there exists a possibility of integrating unstructured, semi-structured and structured data. Data to be mined in big data will be huge in terms of terabytes, petabytes etc. This is one problem for the integration tools to integrate high volume and variety of data. Reliable and High quality data should be integrated and transformed to standard form.

- b. Preprocessing: Since large data to be pre-processed due to Velocity of Big Data, the pre-processing tools or applications should be able to process the data in minimal time and to convert into standard form. Data scaling should be handled properly. Since large data is being stored and taken for the pre-processing, reliable and accurate data only to be taken.

- c. Data mining: data mining algorithms should be able to process the huge amount of data and Variety of the data should be handled appropriately to extract the interesting patterns in minimal time. Here

sophisticated data mining algorithms are needed which will process the data at faster rate. Also people working on this domain should be highly skilled in processing and extracting interesting patterns.

d. Evaluation and Interpretation: The patterns should be evaluated effectively and should be presented visually which will increase the end user knowledge. Presenting the data in visual way in an effective manner and the people involved in the processing and presentation of the visualized data is an important factor in mining big data. Appropriately visualized data will provide the value to the data being mined and helps in increasing the business market. Visualization tools are more important in presenting the data patterns. Visualization tools that we are using should be appropriate and capable of handling and processing high loads of data.

### B. Mining Big Data – Prospects & Applications

With the invent of internet, services nowadays are provided over the internet and with the social networking activities on day to day, large amount of data is being generated and stored in in the data bases in various formats. Integrating such data to understand the insights of the data and hence to understand the needs of the user and the trends in usage, Big data mining is playing a vital role.

Nowadays various organizations investing huge amounts in storing and processing of historical and real-time data as the decision making process is going towards the data centric and accurate decisions need to be taken based on the historical and real time data which is available. Lot of research work is going on towards data integration and effective visualization of qualitative patterns to be extracted.

Since Big data mining is an interdisciplinary, it has significance in various sectors in decision making process. It is generating huge amount of business returns [12].

The following figure illustrate the trend in Big Data market forecast

Figure 5: Big data Forecast (Source: Wikibon 2012)

Some of the applications [7, 8, 13, 14] of big data mining are:

- 1. Social networking Based on user access patterns and data being used and generated, User Profiles can be analyzed effectively and the web pages can be personalized.

- 2. *Manufacturing*—Product modeling, quality and performance of the products can be analyzed and hence to customize the product to meet the customer needs.

- Weather forecasting Time series data can be analyzed effectively which helps in weather forecasting so as to alert the people and governments in case of natural disasters and other calamities.

- 4. *Marketing Research* Product Reviews by the customers can be analyzed which helps in Sales Promotion, pricing and increasing the sales. It also, helps in understanding user buying behavior and sentiment analysis

- 5. Advertising & Brand Promotion Designing the advertisements based on perspective of product performance and promoting the brands to retain the customers and also to create new customer base.

- 6. *BioInformatics*—Biological and genetic data like DNA sequence, protein sequence etc. can be analyzed in classification of species.

- 7. Financial Data Analysis To detect the uncertainty and fraud in the financial data

- 8. *Healthcare* To understand various vital statistics to classify the patients and disease level. Also helps in understanding the effectiveness of the drugs being given to the patients in curing the disease.

- 9. *Government & Political* Evaluate the policies being implemented and the trend of the resources and budget being utilized can be analyzed.

- 10. Retailing Managing the customer relationships and understating the user's needs and pricing modeling can be done.

- 11. Energy Operation modeling can be done.

- 12. *Media & Telecommunications* Network Optimization and fraud detection can be done.

### **CONCLUSIONS**

During the next few years also Big Data is going to grow and continue since the need of the historical data and the management of real-time data which is generating in huge volume, which helps to understand the insights of the data and the user requirements to enhance the products and services so as to retain their space by the organizations in the global market since decision making is becoming data centric. Efficient Analytical Architecture is needed to handle the various problems that we discussed in this paper and the proper management of the variety of data being stored and the efficient visualization tools are also needed to improve

the visual appeal of the data insights which will improve the knowledge being mined. Big Data is becoming the new Final Frontier for scientific data research and for business applications and contributing to data science research.

### **FUTURE DIRECTIONS**

Business Analytics and Big Data Tools need to be reviewed to get further insight into the research areas of Mining and visualizing Big Data.

### REFERENCES

- Big Data Visualization: Turning Big Data Into Big Insights

A White Paper, Intel IT Center, Intel, March 2013

- [2] Dennis McCafferty, "Data Visualization: Making Sense of Big Data", Baseline Magazine, April 2014.

- [3] Big Data: A New World of Opportunities, NESSI White Paper, December 2012.

- [4] Mrs. Deepali Kishor Jadhav, "Big Data: The New Challenges in Data Mining", International Journal of Innovative Research in Computer Science & Technology, Vol 1, Issue 2, Sept 2013, pp. 39-42.

- [5] Yuri Demchenko, "Defining the Big Data Architecture Framework", University of Amsterdam, July 2013.

- [6] Zhong Li, "Harness Big Data Value and Empower Customer Experience Transformation", Infosys Labs Briefings, Vol. 11, 2013, pp. 27-34.

- [7] Katina Michael, Keith W. Miller, "Big Data: New Opportunities and New Challenges", IEEE Computer Society, Vol. 46, Issue No. 6, June 2013, pp. 22-24.

- [8] Alexandros Labrinidis, H. V. Jagadish," Challenges and Opportunities with Big Data", Proceedings of the VLDB Endowment, Vol. 5, No. 12, pp. 2032-2033.

- [9] Big Data Strategy Issues Paper, © Commonwealth of Australia, 2013.

- [10] Divyakant Agrawal, et.al "Challenges and Opportunities with Big Data" – A community white paper, United States, March 2012. http://cra.org/ccc/docs/init/bigdatawhitepaper.pdf

- [11] E. Letouzé, "Big Data for Development: Opportunities & Challenges", May 2011.

- [12] The Emerging Big Returns on Big Data A TCS Global Trend Study, 2013.

- [13] Wei Fan, Albert Bifet, "Mining Big Data: Current Status, and Forecast to the Future", SIGKDD Explorations, Volume 14, Issue 2, pp. 1-5.

- [14] J. Manyika, M. Chui, B. Brown, J. Bughin, R.Dobbs, C. Roxburgh, and A. H. Byers. "Big data: The next frontier for innovation, competition, and productivity", McKinsey Global Institute, May 2011.

- [15] Chris Snijders, Uwe Matzat, Ulf-Dietrich Reips, "Big Data: Big Gaps of Knowledge in the Field of Internet Science", International Journal of Internet Science, Vol. 7, 2012, pp.

### Design And Implementation Of A Cyclic ADC For CMOS Image Sensors

O. Venkata Krishna<sup>1</sup>, B. Janardhana Rao<sup>2</sup>

<sup>1</sup>CVR College of Engineering/EIE, Hyderabad, India

Email: venkatakrishna.odugu@gmail.com

<sup>2</sup>CVR College of Engineering, Hyderabad, India

Email: janardhan.bitra@gmail.com

Abstract— The constant strive for improvement of digital video capturing speeds together with power efficiency increase, has lead to tremendous research activities in the image sensor readout field during the past decade. The improvement of lithography and solid-state technologies provide the possibility of manufacturing higher resolution image sensors, as possibilities for reduced power they provide consumption and integration of complete on-chip cameras. With the increase of image sensors' resolution and frame rate, traditional serial readout schemes become more laborious to design and in many cases simply unachievable for certain required readout speeds. This transfer however imposes additional demands to parallel ADC designs, mainly related to achievable accuracy, area and power.

In this paper a 12-bit Cyclic ADC (CADC) is designed and implemented in 180nm CMOS technology aimed for column-parallel readout implementation in CMOS image sensors. The multiple CADC sub-component architectures and few various Multiplying DAC (MDAC) structures have been re-examined and implemented. Three comparator architectures have been explored and a dynamic interpolative Sub-ADC is presented. Finally, some weak spots degrading the performance of the carried-out design have been analyzed. As an architectural improvement possibility two MDAC capacitor mismatch error reduction techniques have been presented.

*Index Terms*—ADC, DAC, Sensor, CMOS, Low power, Switched Capacitor, Comparator.

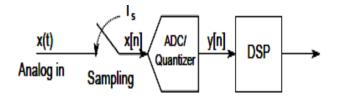

### I. INTRODUCTION

The target of this paper is to design an algorithmic, also commonly known as cyclic, ADC architecture for the purpose of its implementation in a column-parallel readout CMOS image sensor. With the increase of image sensor's resolution and frame rate, traditional serial readout schemes become more laborious to design and in many cases simply unachievable for certain required readout speeds.

A possible solution to this problem is the usage of multiple parallel working ADCs, in order to relax the speed requirements of the otherwise standalone data converter. This solution to the problem however, as in any technological problem has its advantages, challenges and disadvantages. One of the challenge points in column-parallel ADCs appear to be the tight silicon area and power consumption requirements. As various ADC architectures exist, among the compact ones strike to be the algorithmic (cyclic) ADC. The most relevant reasoning about the conduction of this study on cyclic ADCs is the low area requirements as well as the reasonably high resolutions and conversion rates achievable with this type of converters.

Historically the first trials of image sensor developments date back to 1969, when Willard Boyle and George Smith at Bell Labs invented the first chargecoupled device (CCD), which a few years later was implemented in the Hubble Space Telescope [2]. In the same decade range a non-charge-transfer imaging device, as we know it nowadays as CMOS image sensor, was introduced. Even though that both technologies are based on converting photons to electrical charges, CCD based image sensors gained higher velocity due to the fact that they provided much better imaging qualities with the existent semiconductor technology. In the later years, starting late 1980s, with the development of high precision lithography and silicon purification technologies, CMOS image sensors gained popularity, as they provide possibilities for reduced power consumption and integration of complete on-chip cameras. The most important pixel parameters of the image sensors required as input data for the ADC design, Output range, Integration (exposure) time, Reset time and Noise boundary.

The Table 1. lists the main imposed ADC requirements for this work. The provided specifications have been kept in mind during the design. The required sampling speed has been set to comply with a readout speed of 60 frames per second on a 1080p vertical resolution sensor utilizing digital correlated double sampling.

| Parameter              | Value | Unit |

|------------------------|-------|------|

| Resolution             | 12    | bits |

| Sampling Rate          | >130  | KSps |

| Integral Non-Linearity | <10   | LSB  |

| Differential Non-      | < 0.5 | LSB  |

| Linearity              |       |      |

| Power Consumption      | 300   | μW   |

| Supply Voltage         | 3.3   | V    |

| Technology             | 180   | nm   |

| Area                   |       | μm   |

TABLE I SPECIFICATIONS OF ADC

#### II. DESIGN AND IMPLEMENTATION OF CYCLIC ADC

A broad seek for simple architectures incorporating digital correlated double sampling (Digital CDS) and no need for the pixel's signal pre-conditioning was performed. A few attractive architectures in literature were found [5],[4] & [7], in a sense that all of them incorporated the fore-mentioned basic functionality, combined with simple choice of circuitry, namely single-ended MDAC designs. The reasons for the hunt after simplified circuits employing single-ended schematics, stood behind the main design limit, which is the narrow column pitch in high resolution image sensors 2 to 6  $\mu m$ , demanding very low area designs. To achieve high frame rate and high resolution from a sensor, could practically only be achieved with the column-parallel readout architecture.

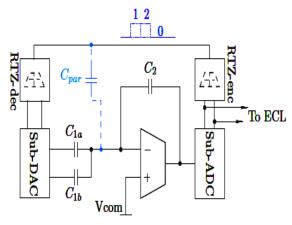

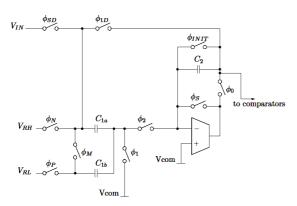

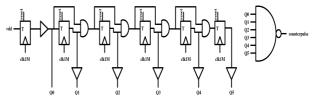

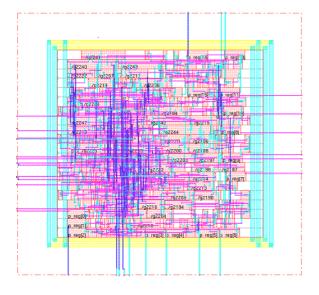

This section aims to give an overview of the proposed ADC. The block diagram of the cyclic converter shown on Figure 1. The converter utilizes an almost similar single-ended MDAC structure but, in this split of the sampling capacitor into two sub-capacitors allowing the generation of the mid-reference locally. The converter utilizes the popular 1.5 bit redundant signed digit conversion, thus allowing for relaxed comparator offset requirements by utilizing a digital error correction.

Figure 1. The Principal diagram of Cyclic ADC architecture.

One major disadvantage with respect to the circuit's performance of the proposed MDAC architecture is its single-ended nature. A differential structure would typically be more insensitive to common-mode noise and provide a more stable readout and parasitic insensitiveness. However due to the additional circuit complexity and two extra sampling capacitors as well as switches required, it appeared to tilt the scales towards a single-ended architecture. While in an isolated case a single-ended structure would give much worse performance results, in a mutual aid with Digital CDS as well as the RTZ coding technique, could potentially provide enough noise independence and accuracy to suit for a 12-bit column-parallel ADC.

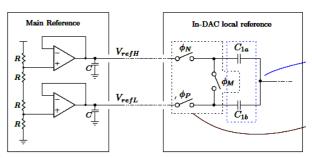

### A In-DAC mid-reference generation scheme

The in-DAC reference generation Figure 2. proposed by [5], practically utilizes the MDAC sampling capacitor as a capacitive divider during the feedback phase to generate the third mid-reference locally from the fed-in *VrefH* and *VrefL*.

Figure 2. Local in-DAC mid-reference generation.

Apart from the obvious silicon area improvement advantage, by relaxing the requirements of the external voltage reference block or in other words removing one extra required reference voltage to be routed, this internal generation scheme allows for a more accurate mid-reference generation, regardless of the absolute values of the *VrefH* and *VrefL* references. Of course all these statements imply that such resulting converter linearity improvements with this scheme would be possible only by having highly matched sampling capacitors.

### B RTZ coding scheme for parasitic sensitivity relaxation

While a fully differential configuration is less sensitive to parasitic coupling of the feedback signals from the sub-ADC, a single-ended structure can not boast with such an advantage. Theoretically the differential MDAC should be 4/6 times less sensitive to parasitic or to formulate it, the error voltage due to parasitic coupling to the summation node will be equal for a single-ended case to:

$$V_{err} = \left(\frac{C_{par1}}{C_2} and D_0 + \frac{C_{par1}}{C_2} and D_1\right) V_{data-line}$$

Although it might be possible to guard the data lines with an extra metal for wider-pitched columns, the authors proposed a return to zero (RTZ) encoding scheme for an effective reduction of the parasitic coupling to the charge summation node. The principal diagram of the ADC architecture on Figure 1. gives an outline of the RTZ coding scheme. The thermometer code from the Sub-ADC is encoded into a pulse width modulated signal, which is quickly transmitted before the very end of the feedback phase. In this way the effect of the parasitic couplings to the charge summation nodes is reduced practically to almost zero. The parasitic effect from these nodes will only be dependent on the transmission speed of the pulse-width encoded signal.

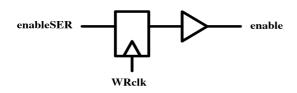

### C The MDAC in details

This section aims to provide a detailed analysis of the re-examined MDAC implemented by [5] and comment on its advantages and disadvantages. As a start Figure 3. shows a principal schematic of the MDAC, built-up around an operational transconductance amplifier. An OTA is a common choice for applications with small capacitive loads, as the case of the MDAC is, due to a row of reasons, standing behind the circuit simplicity of an OTA, or mainly the lack of an output buffer stage in comparison with most OPs.

Figure 3. Principal schematic diagram of the MDAC.

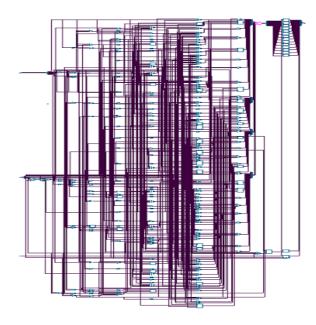

The MDAC structure differs slightly from the "Modified Flip-Around" structure, apart from the split sampling capacitor allowing for internal mid-reference generation, the structure halves the accommodated OTA offset. This results in a global ADC offset, which should not be troublesome and in addition the DCDS technique should fully cancel-out such offset. To go through the functionality of the MDAC we can look at the separate sub-phases and perform a charge redistribution analysis. Figure 4. shows the 4 basic modes of operation of the MDAC.

Figure 4. Detailed MDAC configurations for the four phases.

### D Functional analysis

Before performing signal sampling, in order to make sure that there is no residual charge from previous conversions and make sure all conditions are the same for every CDS step, all capacitors are reset for a short period of time, Figure 4 a). After completion of this phase, signal sampling can start, Figure 4 b). This implies that the charge stored in the capacitors would be:

$$\begin{aligned} q_{1a}(t) &= (V_{in} - V_{com} + V_{os})C_{1a} \\ q_{1b}(t) &= (V_{in} - V_{com} + V_{os})C_{1b} \\ q_{2}(t) &= (V_{in} - V_{com} + V_{os})C_{2} \end{aligned}$$

During the next - feedback phase, Figure 4. c) the sampled signal is amplified by two. Here is the place to mention again that the accumulated offset during sampling will appear as a global ADC offset with half the magnitude of the OTA offset, as capacitor C2 had stored the offset in the previous phase and during the present phase is connected in the feedback loop, thus the amplifier would have added half the OTA offset. The fourth phase performs the analogue subtraction. Depending on the decisions taken during the feedback phase by the Sub-ADC, the top plates of C1a and C1b are connected to the reference voltages.

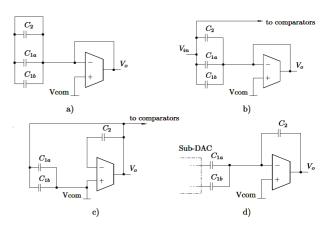

### III. COMPARATOR IMPLEMENTATIONS

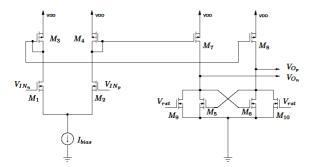

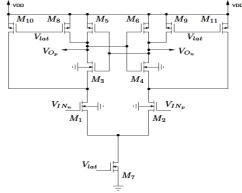

### A Static latched comparator.

To begin with a simple static latched comparator is shown on Figure 5 as proposed by [3]. Transistors *M*1, *M*2, *M*3 and *M*4 are forming a differential amplifier, which controls the current flow through the latch composed of transistors *M*5 and *M*6 via the control transistors *M*7 and *M*8. The decision is taken when the reset transistors' *Vgs* is pulled down, thus releasing the latch from reset state, depending on the currents flowing through the differential pair, thus the two latch

branches, one of the transistors M5 or M6 switch on first and trigger the regeneration.

Figure 5. A principle schematic diagram of a simple static latched comparator.

The simple static implementation candidate shown on Figure 5 has some advantages and disadvantages as compared to dynamic comparator implementations. As the currents flowing through the latch transistors are well defined by the biasing current, the comparator's speed can be very easily controlled, however the between connection speed and static consumption is very closely tight. As it is crucial to keep low power consumption in a column parallel ADC, this architecture does not allure a great interest due to its low efficiency. The architecture provides a somewhat more adequate kickback noise performance, comparison with some dynamic implementations as we shall see further. The differential amplifier and the current mirroring transistors provide a very good isolation between the latch pair. These however may have a speed reduction effect due to the additional capacitive load overhead i.e. an additional pole added at the drains of the differential pair diode loads.

### B Class AB comparator.

An architecture, very similar in a functional point of view to the first static candidate is shown on Figure 6.

Figure 6. A semi-static often referred to as Class AB comparator.

In order to increase the comparator's speed the semistatic or often referred to as Class AB comparators, do not rely on keeping the latch in reset by holding the reset transistors on, as was the previous case with the static comparator in Figure 5. Instead to reduce the static current drawn by the latch a complementary latch pair is utilized (transistors M3, M4, M5 and M6) together with a switchoff transistor M8. Shortly, when Vlat is low, the only current path flows through the differential pair, transistor M7 is on, which keeps the upper latch (transistors M3 and M4) in reset. When Vlat is triggered high, M7 turns off, meaning that the upper latch's regeneration is triggered. At the very same moment M8 turns on and the bottom pair's drain currents start increasing depending on the upper latch's tilt. This implies that the output should be driven much faster, as there is no intentional current limitation. A major drawback of this architecture as also described by [5] appears to be the increased kickback noise at the inputs, since the differential pair's drains are capacitive coupled directly to the output nodes, which jump back and over from rail to rail. In addition, a hidden effect, decreasing comparator's accuracy, potentially introducing higher metastability issues is the reset transistor M7. When turned off, its residual channel charge will flow to both output branches, which may not be with equal impedance nor voltage level, therefore setting unequal starting conditions for the regeneration latch. This would imply that the Class AB stage would potentially have higher offset dependency, as if the regeneration latch transistors M5 and M6 are mismatched, the effect of charge injection from M7 will be amplified.

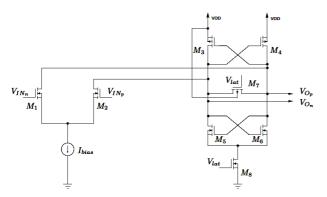

### C A dynamic implementation

A major drawback in the static implementations described in the previous section is the poor power efficiency as well as relatively low speeds. A solution to the power efficiency problem appear to be the dynamic implementations. Figure 7. shows a dynamic comparator implementation using two inverter gates as a regeneration latch.

Figure 7. A dynamic comparator implementation.

It could be noted that transistor M7 when Vlat is kept low, completely turns off the whole circuit and only the leakage currents through M7 contribute to the

total power consumption at this phase. Transistors *M*8, *M*9, *M*10 and *M*11 keep the inverters consisting of *M*3, *M*5, *M*4 and *M*6 reset and ensure equal starting conditions for both of them. When *Vlat* is triggered high, *M*7 starts conducting, the reset transistors *M*8, *M*9, *M*10 and *M*11 switch off and the regeneration process starts. When the inverters settle, there is no current flowing through the system, besides the DS leakage currents flowing though the inverters. The output voltage range of this dynamic implementation is however limited in the lower end by the DS drops over the differential pair transistors *M*1, *M*2 and the tail switch

M7, thus the architecture does not ensure full rail-rail output range. This implies that if full swing is required some level restoration circuits must be used, in its simplest example this could be an inverter stage. The kickback noise generated from this architecture seems to be comparable with the AB stage. The differential pair is closely coupled with the output nodes, only M3 and M4 provide insignificant insulation, as their VD is also expected to jump up-down. The dynamic implementation

besides the static offset from the differential pair, will also be susceptible to larger dynamic offset due to the charge injection (CI) and clock feed-through of the switches. The particular structure on Figure 7. would possibly have somewhat relaxed CI effect, as the reset transistors M8, M9, M10 and M11 would, to a large extent, cancel-out the charge influence on the inverters. M10 and M11 would inject charge on the source nodes of M3 and M4, while M8 and M9 would do on the drains of M5 and M6. This however is a very idealistic and difficult to define effect, as in reality there would be a clock skew and respectively turn-off time between all reset transistors, which makes the analysis difficult to follow.

### D The Sub-AD comparator implementation

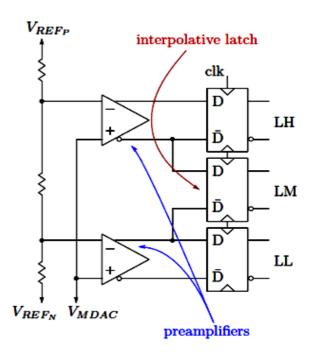

Due to its power efficiency the fore mentioned dynamic implementation was chosen as the basic building block of the Sub-AD module. In addition a voltage reference interpolation technique has been used to ensure higher reliability for the cost of a few additional elements and a small increase in power consumption.

As the dynamic implementation offers lowest power consumption and moderately high offset, which is acceptable, it appeared to be the most attractive architecture among the above-described. As an additional improvement possibility, implementing an interpolative Sub-AD was also possible with the chosen dynamic architecture, for the only cost of an additional latch stage as proposed by [23].

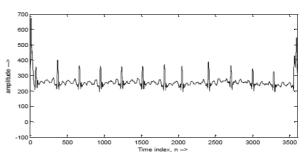

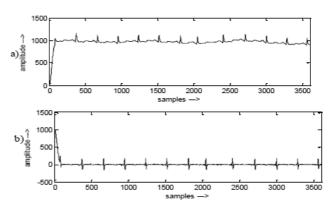

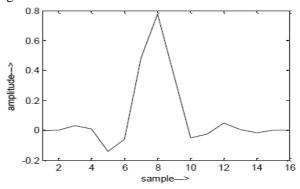

Figure 8. Sub Flash AD Comparator Interpolation Technique

To start with, the basic interpolation idea is clarified on Figure 8. The preamplifiers amplify the difference between the fed-in voltage from the MDAC and the generated sub-references, for further decision from the latches. We can clearly see that the two neighboring shoulders of the differential amplifiers could be used for generating an additional decision level for the cost of an extra latch. Figure 9. shows the outputs of two differential amplifiers hooked-up in a configuration as shown on Figure 8. with a swept input node close to the reference voltage levels. Practically interpolative latch, will be triggering on the midreference which should be equal to:

$$V_{REF_{M}ID} = \frac{V_{REF_{H}} + V_{REF_{L}}}{2}$$

The main drawbacks of this implementation stand behind the required balancing of the unequal loading of the differential pairs, as this may create a static design-inherited offset and also create a higher linearity requirement. The extra preamp loads also add additional poles and in general such interpolative structures are slower. In the case with the current application, requirements on the comparator's speed are somewhat relaxed and utilizing interpolation does not cause additional issues with respect to speed. The principle schematic on Figure 8. aims to present the interpolation technique in the voltage domain, this however in the case of the chosen fully dynamic comparator would be transferred into the current domain, as all the current flows through the differential pairs.

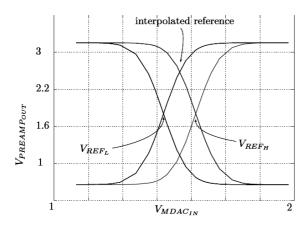

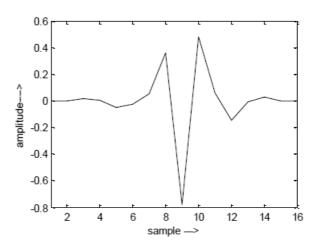

Figure 9. Mid-reference interpolation output voltages of two differential amplifier stages in a function of a linearly swept input voltage, hooked-up following the configuration on Figure 8.

To give a final summary of the designed dynamic comparator's performance for the Sub-AD module, Table 2. shows the main measured parameters. It should be noted that the comparator's design would most probably require modifications after parasitic extraction estimations and/or layout. A design of a comparator fulfilling the requirements in all corners, including parasitic sensitiveness prediction could be a very time-consuming task. As the scope of this thesis is to explore the proposed architecture and possibly improve it, full corner and parasitic optimizations are to be further explored.

TABLE II SUMMARY OF THE MAIN MEASURED COMPARATOR PERFORMANCE PARAMETERS

| Symbol            | Parameter                     | Min | Typical | Max | Unit |

|-------------------|-------------------------------|-----|---------|-----|------|

| $\Delta V_{os}$   | Input Offset<br>Voltage Drift | -58 | 3       | +61 | mV   |

| T <sub>d</sub>    | Response<br>Time              | -   | 118     | i   | ns   |

| $\sigma_n$        | Noise variance                | -   | 0.48    | -   | mV   |

| $\delta_{min}$    | Resolution                    | -   | 0.317   | -   | mV   |

| V <sub>supp</sub> | Supply<br>Voltage             | -   | 3.3     | -   | V    |

| $P_{dyn}$         | Dynamic<br>Power              | -   | 6       | -   | μW   |

| P <sub>stat</sub> | Static Power                  | -   | 0.224   | -   | μW   |

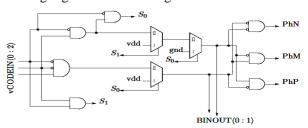

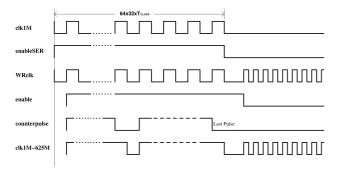

### IV. SUB-AD CONTROL LOGIC

As the code provided by the comparators is thermometer-encoded and an RSD representation output is required, certain encoding logic had to be introduced. In addition the Sub-AD logic has the task to control the MDAC and determine the In-DAC switch states during the next feedback phase. In the previous subsection an interpolation technique for the comparators was introduced, thus effectively forming a 2 bit Sub-AD. As

this extra half bit was introduced for reduction of an error probability, it is the Sub-AD logic that needs to convert the three thermometer encoded comparator levels to binary 1.5 bit RSD. Table 3. shows a truthtable of the implemented Sub-AD logic.

TABLE III A TRUTH TABLE OF THE IMPLEMENTED SSB-AD LOGIC

| vCODEIN<0:2> | BINOUT<0:1> | $P_HP$ | $P_HM$ | $P_HN$ |

|--------------|-------------|--------|--------|--------|

| 000          | 00          | 1      | 1      | 0      |

| 001          | 01          | 1      | 0      | 1      |

| 011          | 01          | 1      | 0      | 1      |

| 111          | 10          | 0      | 1      | 1      |

| 100          | 00          | 1      | 1      | 0      |

| 010          | 01          | 1      | 0      | 1      |

| 110          | 10          | 0      | 1      | 1      |

| 101          | 00          | 1      | 1      | 0      |

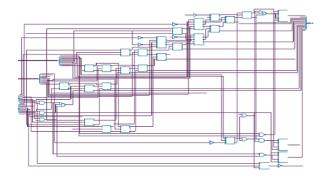

As a reference, the hardware implementation of the encoding logic is shown on Figure 10.

Figure 10: A principal logic diagram of the implemented Sub-AD encoding control logic.

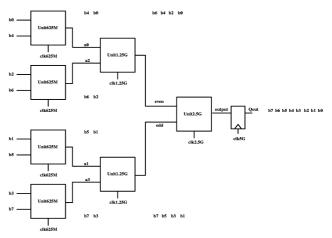

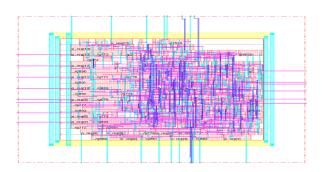

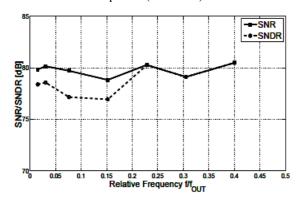

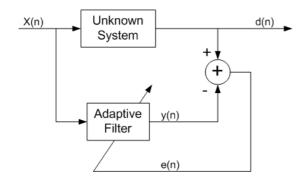

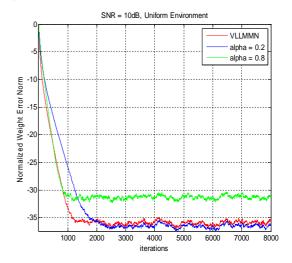

### V. RESULTS

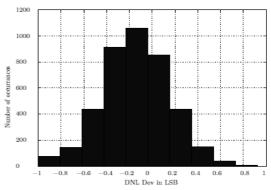

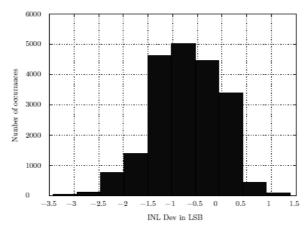

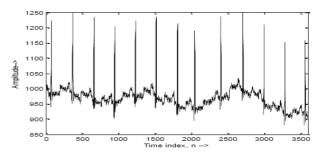

In this section of the paper, The main ADC performance parameters concerning image sensors were introduced. In order to estimate the converter's performance from linearity point of view, transient noise simulations based on multiple samples per code were performed, following the IEEE 1241 standard [1]. Figure 11. And figure 12. shows distribution histograms of the differential and integral non-linearity simulations.

Figure 11. Differential Non-Linearity deviation distribution.

Figure 12. Integral Non-Linearity deviation distribution.

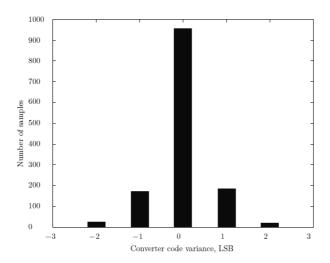

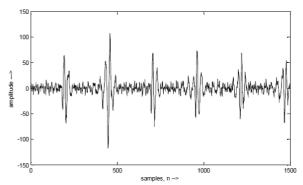

The random noise of an ADC is the excursive fluctuation of its converted digital code word, when an ideal noise-free signal is applied at its input. In the case with the current application, the random ADC noise would appear as a spatial image noise and is thus an important degradation index. The currently performed random noise tests were performed following the IEEE1241 Method 4.5.3.1 standard [1]. Practically following that standard the noise variance was estimated. Figure 13. shows a histogram of the acquired logic level differences from sample to sample. An evaluation script was developed using the IEEE1241 Method 4.5.3.1 and Method 4.5.3.2.

To provide an overview of the current state of the converter Table. 4 provides summarized results for the designed converter. These must be only taken as indicative results, as the current design state does not include device mismatch, external reference voltage and Sub-AD reference generation non-idealities.

Figure 13: Simulated random noise variance, estimated by 1500 samples, worst case corner.

### TABLE IV SUMMARIZED PERFORMANCE RESULTS OF THE DESIGNED CONVERTER

| Parameter                   | Value     | Unit |

|-----------------------------|-----------|------|

| Technology                  | 180       | nm   |

| Resolution                  | 12        | bits |

| Sampling Rate               | <150      | Ksps |

| Input Voltage Range         | 1.35      | V    |

| Integral non- Linearity     | +1.5/-3.5 | LSB  |

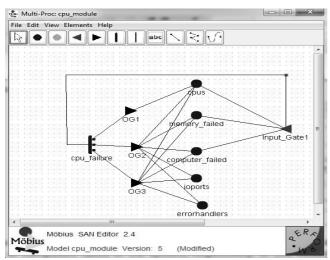

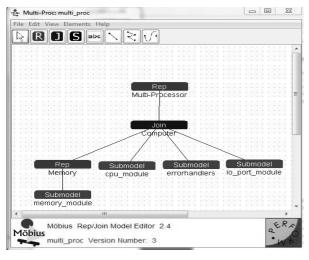

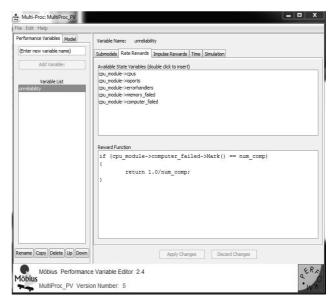

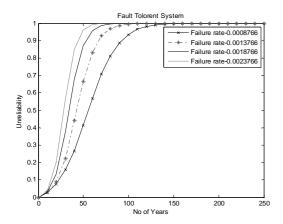

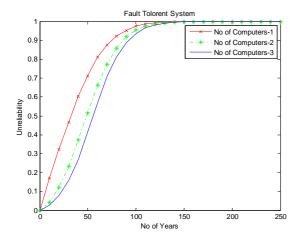

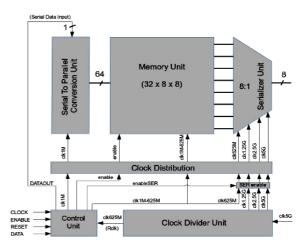

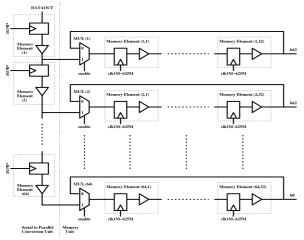

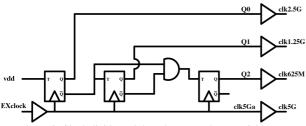

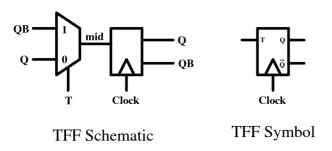

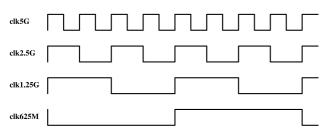

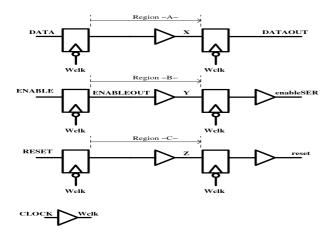

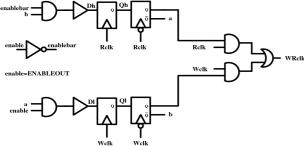

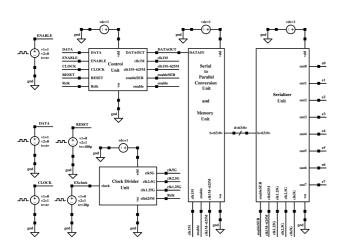

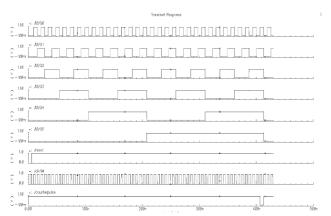

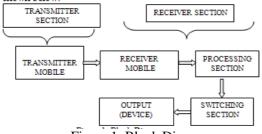

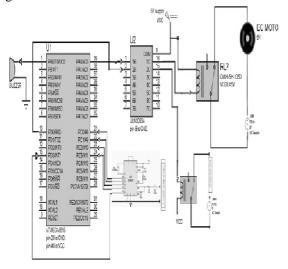

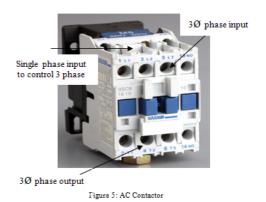

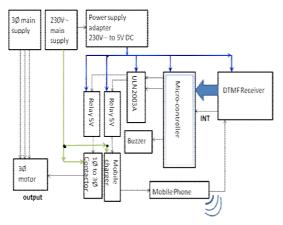

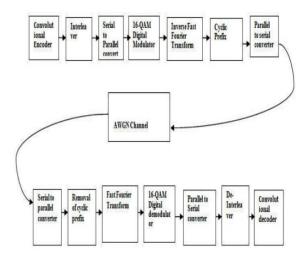

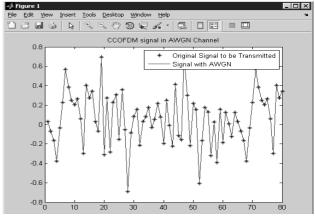

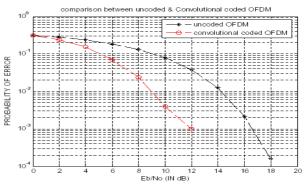

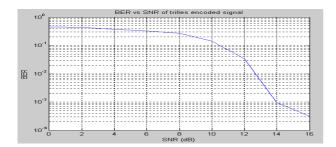

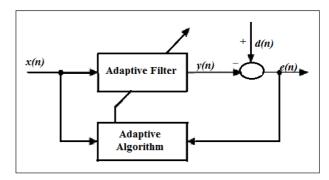

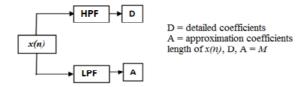

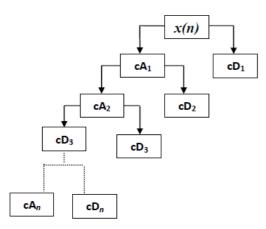

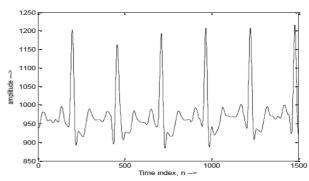

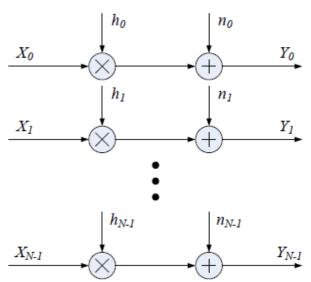

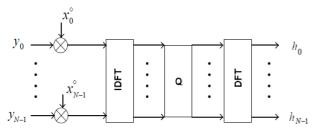

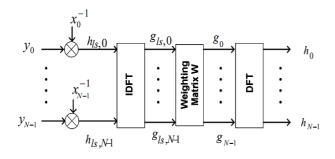

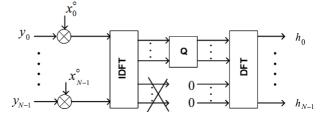

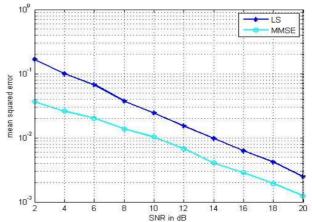

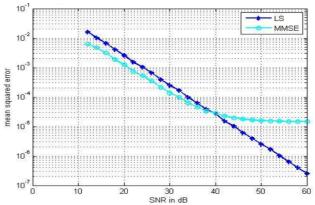

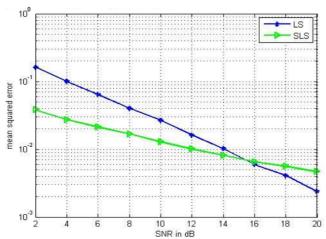

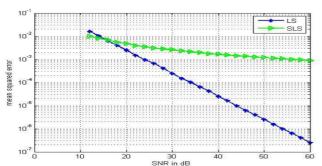

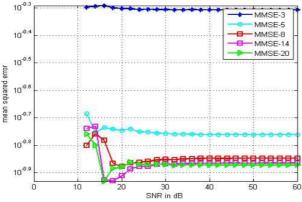

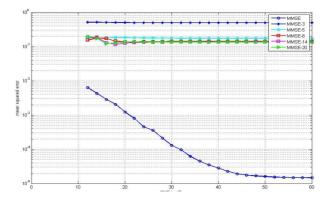

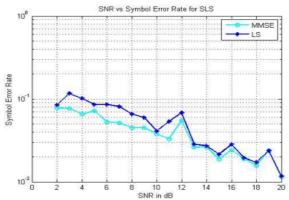

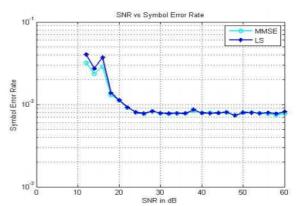

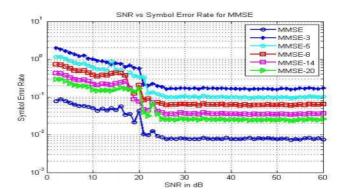

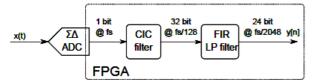

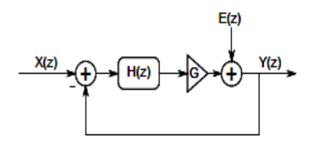

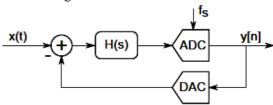

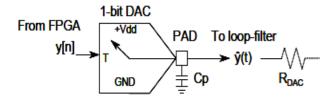

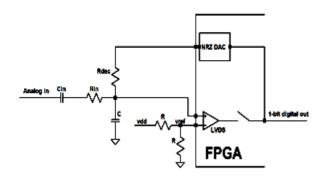

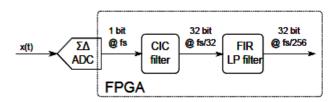

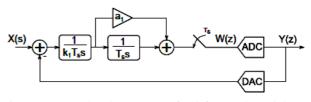

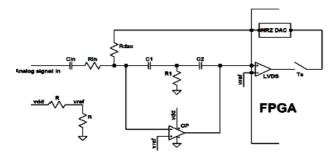

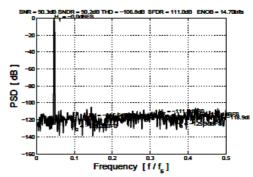

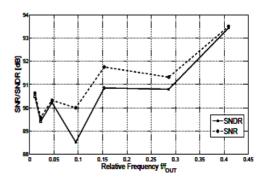

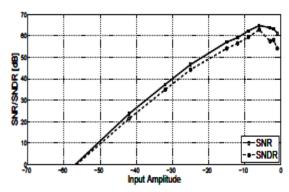

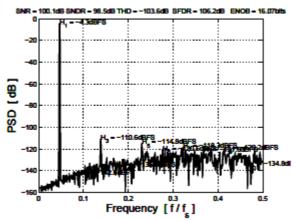

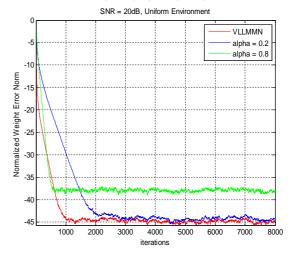

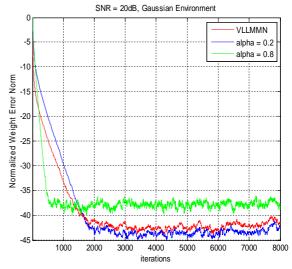

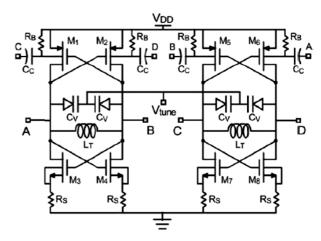

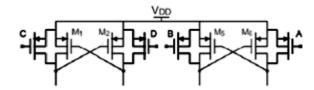

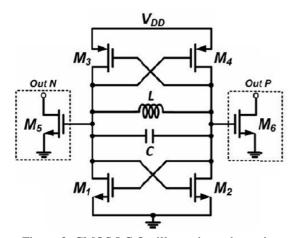

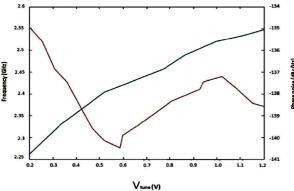

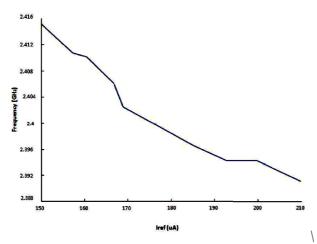

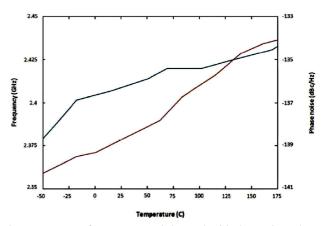

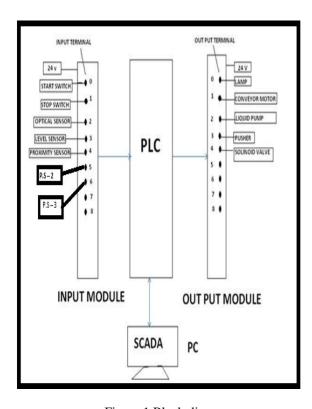

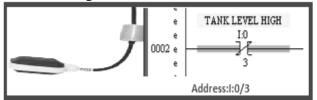

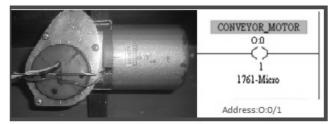

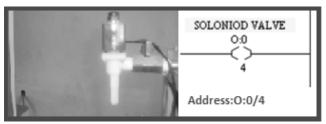

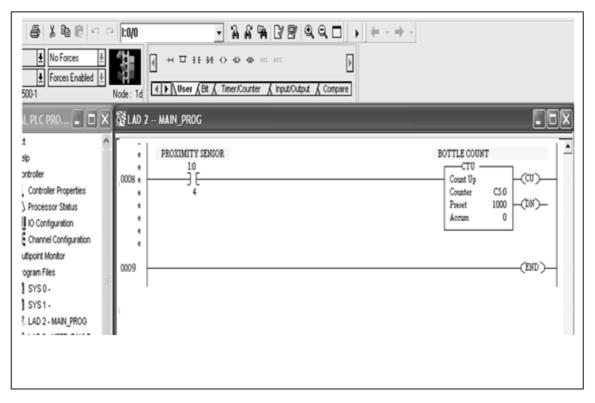

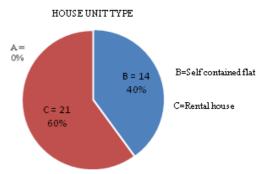

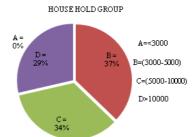

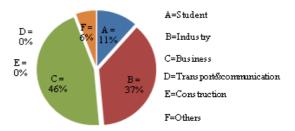

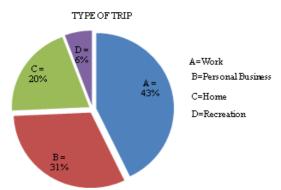

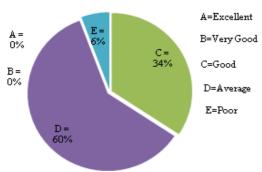

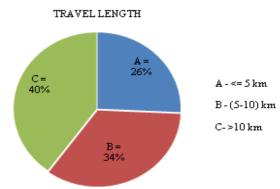

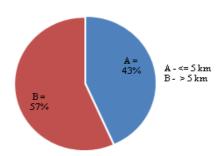

| Differential Non-Linearity  | ±0.8      | LSB  |