# CVR JOURNAL OF SCIENCE & TECHNOLOGY

VOL. NO: 2, JUNE 2012

ISSN 2277-3916

CVR COLLEGE OF ENGINEERING

In Pursuit of Excellence

### **PATRONS**

Dr. Raghava V. Cherabuddi, President & Chairman

Dr. K. Rama Sastri, Director

Dr. A. D. Raj Kumar, Principal

Editor : Dr. K. V. Chalapati Rao, Professor & Dean, Academics

**Associate Editor**: Wg. Cdr. Varghese Thattil, Professor, Dept. of ECE

Editorial Board :

Dr. K. Lal Kishore, Former Director, R&D and Registrar (Retd.), JNTUH.

Dr. S. Ramachandram, Vice Principal, College of Engineering &

Professor Dept. of CSE, Osmania University.

Prof. L. C. Siva Reddy, Vice Principal and Professor & Head, Dept. of CSE, CVRCE

Dr. M. S. Bhat, Professor & Dean, Evaluation, CVRCE

Dr. N. V. Rao, Professor, Dept. of CSE, CVRCE

Prof. R. Seetharamaiah, Professor & Head, Dept. of IT, CVRCE

Dr. K. Nayanathara, Professor & Head, Dept. of ECE, CVRCE

Dr. K. S. Dhanavanthri, Professor & Head, Dept. of EEE, CVRCE

Prof. S. Narayana, Professor & Head, Dept. of EIE, CVRCE

Dr. T. A. Janardhan Reddy, Professor & Head, Dept. of Mech. Engg., CVRCE

Dr. E. Narasimhacharyulu, Professor & Head, Dept. of H&S, CVRCE

# CVR JOURNAL OF SCIENCE & TECHNOLOGY

# CVR COLLEGE OF ENGINEERING

(An Autonomous College affiliated to JNTU Hyderabad)

Mangalpalli(V), Ibrahimpatan(M),

R.R.District, A.P. – 501510

http://cvr.ac.in

### **EDITORIAL**

The Second Volume of the CVR Journal of Science & Technology is being brought out following the same guiding principles of maintaining relevance and excellence in the contributions, as was indicated in the previous Volume. NATIONAL INSTITUTE OF SCIENCE COMMUNICATION AND INFORMATION RESOURCES has registered the Journal and assigned ISSN -2277-3916 based on the quality of contributions in Volume-1. Accordingly the Volume-2 of our Journal includes the ISSN No. on cover page as well as on each page of the Journal.

As was the case for the previous Volume of the Journal, we have received for the current Volume, papers from all the Departments of the College. In addition we have received a few contributions from outside the college. Following review by the Editorial Board, 19 papers have been selected and included in the current Volume. The break-up of contributions from various departments is: CSE-5, ECE-5, EEE-2, EIE-1, H & S-1, IT-2 and MBA-3.

Considering the importance of research culture among staff members in providing quality education to students, it is gratifying to note that our staff members are pursuing active research in addition to their teaching work as is evident from the quality of the papers. The present global picture of technology demands constant updating of knowledge and skills of teachers if they have to provide appropriate guidance to the students. With widespread use of Internet, there is no dearth of information and the students have abundant opportunities to obtain latest knowledge in any area. However they need guidance in appropriate utilization of the knowledge they acquire, as per need in different contexts. It is for the teachers, with their maturity and experience, to provide this kind of guidance. With the experience gained by contributing papers to Research Journals, the teachers would acquire the requisite competence to provide valuable suggestions to the students.

It is our earnest attempt to continue with the publication of the **CVR Journal of Science** and **Technology** on a Bi-annual basis and make every attempt to constantly improve the quality of our Journal. We hope thereby to contribute to the wider cause of serving Engineering Education as per the needs of time.

K. V. CHALAPATI RAO

### **CONTENTS**

| CVR Journal of Science & Technology,                                                                       | Volume 2,          | June 2012            | ISSN 2277-3916 |

|------------------------------------------------------------------------------------------------------------|--------------------|----------------------|----------------|

| Design Patterns For Scheduling Tasks In Real-Ti<br>UVR Sarma, Dr KV Chalapati Rao, Dr P Pren               |                    |                      | 1              |

| Architecture Of Intelligent Process Controlling N<br>Dr Hari Ramakrishna                                   | Model through Ima  | ge Mining            | 6              |

| Pattern Methodology Of Documenting And Com<br>Dr Hari Ramakrishna, Dr K V Chalapati Rao                    | nmunicating Doma   | in Specific Knowledg | ge9            |

| Applying Principles Of LEAN In Academic Env S Suguna Mallika                                               | ironments          |                      | 16             |

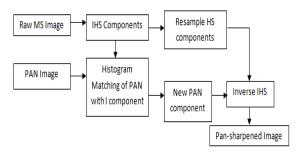

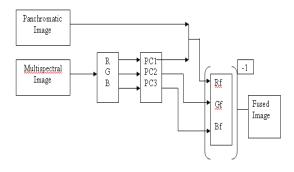

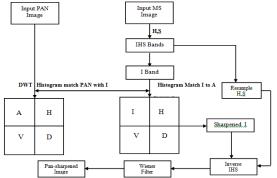

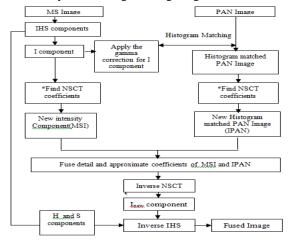

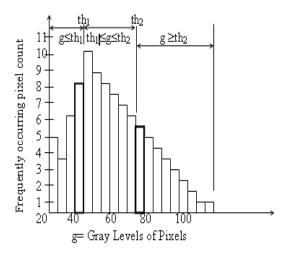

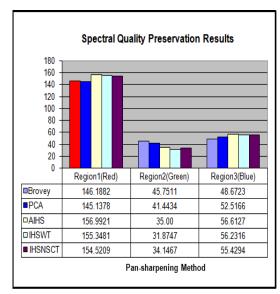

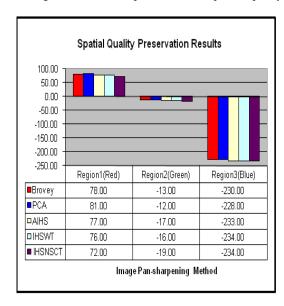

| Region-Wise Quality Measurements Of Pan-shar<br>G P Hegde, Dr I V Muralikrishna, Dr Nagaratna              |                    |                      | 19             |

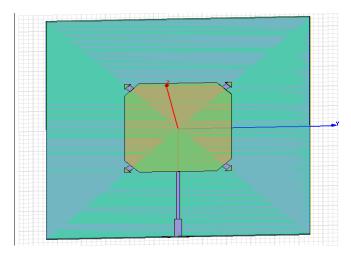

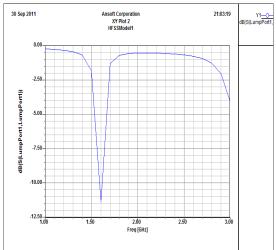

| Polarization Reconfigurable Microstrip Antennas<br>A Bharathi, P Kavitha                                   | s For Wireless Cor | mmunication          | 27             |

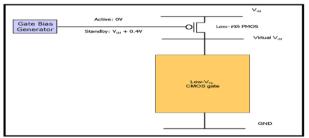

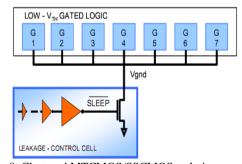

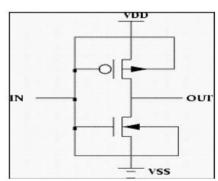

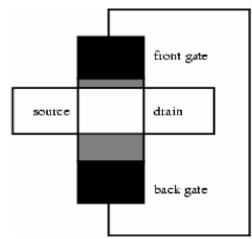

| Technology Scaling And Low Power Design Tec<br>T Esther Rani, Dr Rameshwar Rao, Dr M Asha H                |                    |                      | 30             |

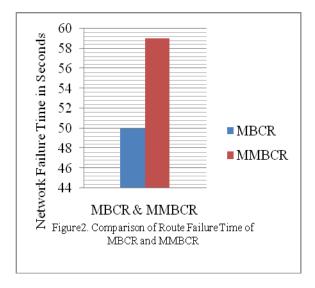

| Globalized Power Aware Routing Protocols For Humaira Nishat, Dr D Srinivasa Rao                            | Mobile Ad Hoc N    | etworks              | 40             |

| Survey On Android OS And C2DM Service R R Dhruva, V V N S Sudha                                            |                    |                      | 43             |

| A Survey On Routing Protocols In Wireless Sens Shakeel Ahmed                                               | sor Network        |                      | 47             |

| Power Quality Improvement Using Interline Unit R N Bhargavi                                                | fied Power Quality | Conditioner          | 51             |

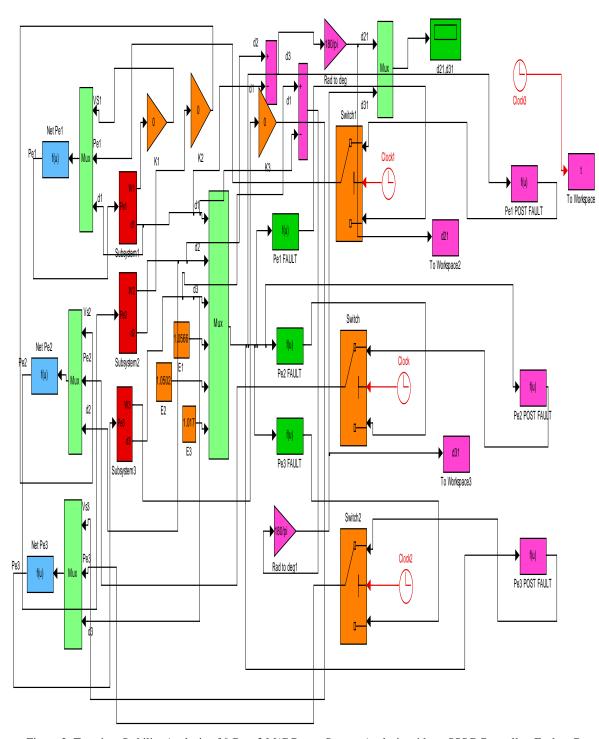

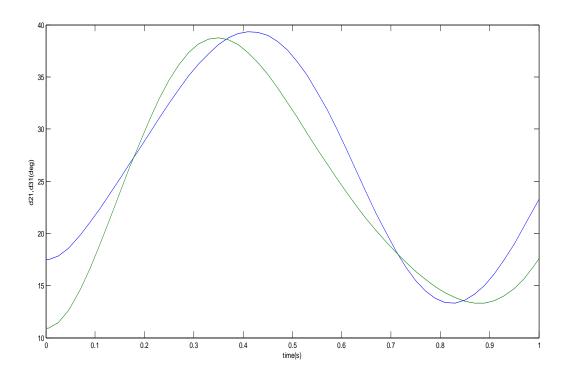

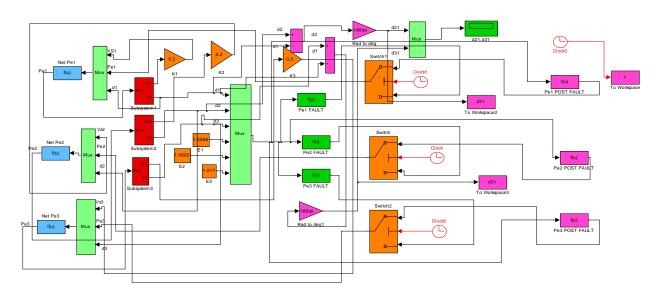

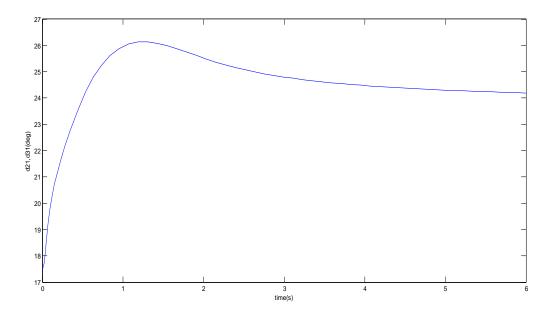

| Power System Transient Stability Analysis With P Nagaraju Mandadi, Dr K Dhanvanthri                        | SSSC Controller-   |                      | 56             |

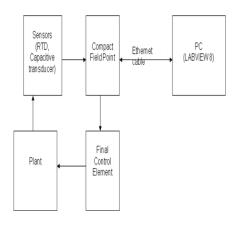

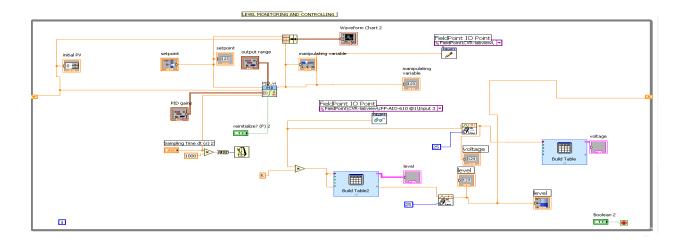

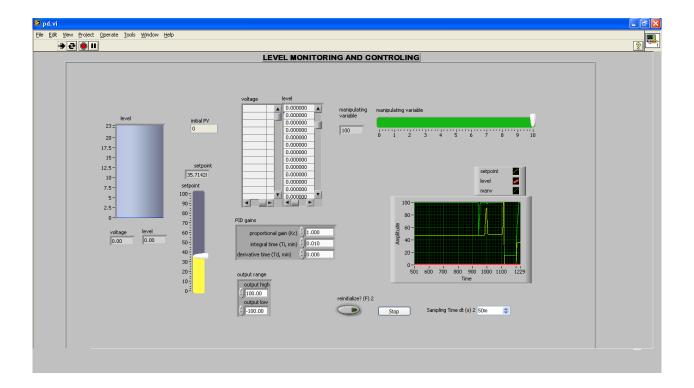

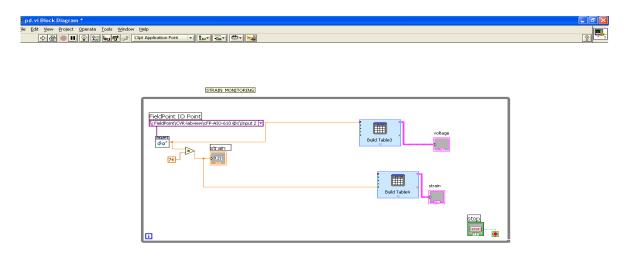

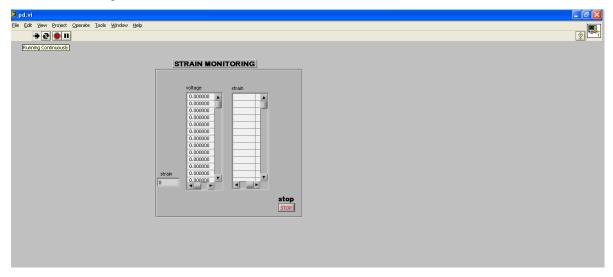

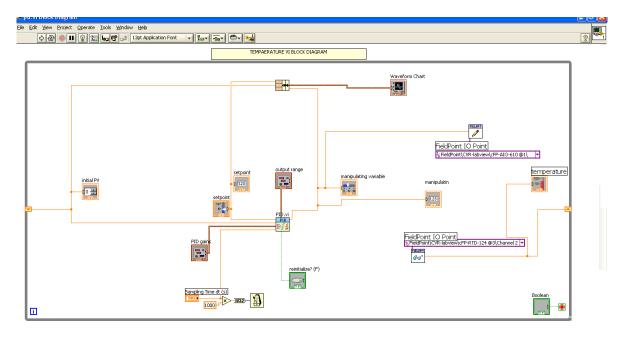

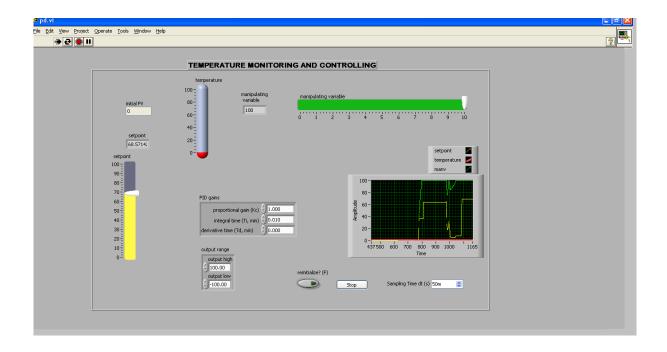

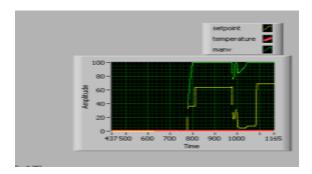

| Control Of Process Variables For Remote Applie S Harivardhagini, S Pranavanand                             | cations Using Lab  | VIEW and Internet    | 61             |

| Numerical Solution Of Oscillatory Motion Of Dusty Memory Fluid Through Porous Media D Sreenivas, B Shankar |                    |                      |                |

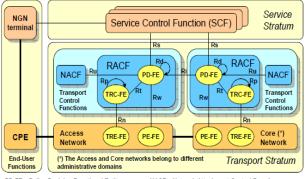

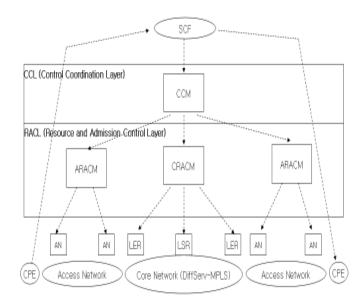

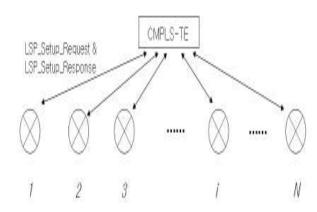

| Next Generation Network— A Study On QOS Me<br>Dr B B Jayasingh, Sumitra Mallick                            | echanisms          |                      | 70             |

| Extended AODV For Multi-Hop WMN S Jyothsna                                                                 |                    |                      | 76             |

| A Study On HR Practices In CVRCE Dr B Archana, Dr M S Bhat                                                 |                    |                      | 80             |

| Queuing Theory-A Tool For Optimizing Hospita <i>V R Girija</i> , <i>Dr M S Bhat</i>                        | l Services         |                      | 86             |

| Effect of Inflation On Various Commodities <i>Lalitha Suddapally</i>                                       |                    |                      | 90             |

# Design Patterns For Scheduling Tasks In Real-Time Systems

U.V.R. Sarma<sup>1</sup>, Dr. K. V. Chalapati Rao<sup>2</sup> and Dr. P. Premchand<sup>3</sup>

<sup>1</sup>CVR College of Engineering, Department of CSE, Ibrahimpatan, R.R.District, A.P., India

Email: sarmauvr@yahoo.co.in

<sup>2</sup>CVR College of Engineering, Department of CSE, Ibrahimpatan, R.R.District, A.P., India

Email: chalapatiraokv@gmail.com

<sup>3</sup>Osmania University, Department of CSE, Hyderabad, A.P., India

Email: profpremchand.p@gmail.com

Abstract—This paper discusses some of the popular design patterns employed in scheduling tasks in various categories of real-time applications and generalizes the guidelines for designing and developing real-time systems. A tool is proposed to automate the application of these patterns when creating a detailed design model.

Index Terms—Design Pattern, Real-Time Systems, periodic, aperiodic and sporadic tasks, EDF, SETF, LETF, Rate-Monotonic Scheduling, Deadline-Monotonic Scheduling, Priority Ceiling, Priority inversion, Least Laxity, Maximum Urgency First.

### I. INTRODUCTION

A *design pattern* is a generalized solution to a commonly occurring problem [1]. It is not a finished design that can be transformed directly into code – rather, it is a description or template, which helps in solving a problem and can be used in many different situations. Good OO designs are reusable, extensible and maintainable. Patterns show us how to build systems with good OO design qualities. Gamma and others, popularly known as Gang of Four (GoF) list 23 design patterns [1]. Usage of design patterns helps to lower software costs.

A system is said to be *real-time* when quantitative expressions of time are necessary to describe the behavior of the system. Usually, there are many real-time tasks in such a system and are associated with some time constraints. A real-time task is classified into either hard, firm or soft real-time depending on the consequences of a task failing to meet its timing constraints. A real-time task is called *hard* if missing its deadline may cause catastrophic consequences on the environment under control. It is called *firm* if missing its deadline makes the result useless, but missing does not cause serious damage and it is called *soft* if meeting its deadline is desirable (e.g. for performance reasons) but missing does not cause serious damage.

Typical Hard RT activities include sensory data acquisition, detection of critical conditions and low-level control of critical system components. Typical application areas are power-train control, air-bag control, steer by wire, brake by wire (automotive domain) and engine control, aerodynamic control (aircraft domain). Typical Firm RT Activities include decision support and

value prediction. Typical application areas are Weather forecast, Decisions on stock exchange orders etc. Typical Soft RT Activities include command interpreter of user interface, keyboard handling, displaying messages on screen, representing system state variables and transmitting streaming data. Typical application areas are communication systems (voice over IP), user interaction and comfort electronics (body electronics in cars).

Appropriate *scheduling* of tasks is the basic mechanism adopted by a real-time operating system to meet the constraints of a task. Therefore, selection of an appropriate task scheduling algorithm is central to the proper functioning of a real-time system.

### II. TYPES OF REAL-TIME TASKS

A task is an executable entity of work, characterized by task execution properties, task release constraints, task completion constraints and task dependencies. Tasks are executed in a system made up of a processor (CPU) and other resources (communication links, shared data etc.)

Task execution properties include Worst-case execution time, Criticality level, Preemptive / non-preemptive execution and whether a task can be suspended or not during execution.

Based on the way real-time tasks recur over a period of time, it is possible to classify them into three main categories: *periodic*, *aperiodic* and *sporadic* tasks.

A periodic task is one that repeats after a certain fixed time interval. Deadlines have to be met with precision, and so they are hard real-time in nature, whereas an aperiodic task can arise at random instants but we can afford to miss few deadlines and hence soft real-time in nature. A sporadic task is one that recurs at random instants and mostly hard real-time in nature.

### III. SCHEDULING APPROACHES

Three commonly used approaches to scheduling Real-Time Systems are [2]:

- 1. Clock-Driven approach.

- 2. Round-Robin approach

- 3. Priority-Driven approach.

### 3.1 Clock-Driven approach (also called time-driven)

In this approach, decisions on task execution are made at specific time instants. All the parameters of the

tasks are fixed and known apriority. Schedules are computed off-line and stored for use at run-time. Hence scheduler overhead during run-time is minimized. H/W timer is used to regularly space time instants. Scheduler selects the task, blocks, and after expiry of timer, awakes and repeats these actions.

### 3.2 Round-Robin approach

This approach follows the fairness principle – justice to all. It is commonly used for scheduling time-shared applications (time slice – in the order of tens of msec). A FIFO queue of tasks ready for execution is maintained. An executing task is preempted at the end of time slice.  $1/n^{th}$  share for n tasks in a round (hence called processorsharing algorithm). A variation to this approach is weighted round robin. Different tasks may have different weights – for ex., a task with weight wt gets wt time slices every round; the length of the round is equal to the sum of the weights of all the ready tasks; weights can be adjusted to speed up / retard the progress of each task.

Round Robin approach is not suitable for tasks requiring good response time, particularly when we have precedence constrained tasks, but suitable for incremental consumption – for ex., UNIX pipe. In case of pipelining, they can complete even earlier – ex: Transmission of messages by switches en route in a pipeline fashion. The approach does not require a sorted priority queue; it uses only a round-robin queue; which is a distinct advantage, since priority queues are expensive.

### 3.3 Priority-Driven approach

These algorithms never leave any resource idle intentionally. Scheduling decisions are made when events such as releases and completion of tasks occur; hence called event-driven. Other names — greedy scheduling, list scheduling and work-conserving scheduling.

Most scheduling algorithms used in non-real-time systems are priority-driven. Examples include FIFO, LIFO – priorities based on release times; SETF (Shortest-Execution-Time-First) and LETF (Longest-Execution-Time-First) – priorities based on execution times. Priority-driven algorithms can be implemented with either preemptive or non-preemptive scheduling. In some cases, non-preemptive scheduling may look attractive, but, in general, non-preemptive scheduling is not better than preemptive scheduling.

Priority-based scheduling systems operate in one of three primary modes:

- 1. Static priority systems,

- 2. Semi-static or

- 3. Dynamic priority systems.

3.3.1 Static Priority System: In a static system, a task's priority is determined at compile time and is not changed during execution. This has the advantages of simplicity of implementation and simplicity of analysis. The most common way of selecting task priority is based on the period of the task, or, for asynchronous event-driven tasks, the minimum arrival time between initiating events. This is called *Rate Monotonic Scheduling* (RMS). Static scheduling systems may be analyzed for schedulability

using mathematical techniques such as Rate Monotonic Analysis.

Another well-known fixed priority algorithm is the *Deadline-Monotonic* (DM) algorithm. This algorithm assigns priorities to tasks according to their relative deadlines: the shorter the relative deadline, the higher the priority. Clearly, when the relative deadline of every task is proportional to its period, the RMS and DM algorithms are identical. When the relative deadlines are arbitrary, the DM algorithm performs better in the sense that it can sometimes produce a flexible schedule when the RMS algorithm fails, while the RMS algorithm always fails when the DM algorithm fails.

3.3.2 Semi-Static Priority System: Semi-static priority systems assign a task a nominal priority but adjust the priority based on the desire to limit priority inversion. This is the essence of the priority ceiling pattern. If a low priority task locks a resource needed by a high priority task, the high priority task must block itself and allow the low priority task to execute, at least long enough to release the needed resource. The execution of a low priority task when a higher priority task is ready to run is called priority inversion. The naïve implementation of semaphores and monitors allows the low priority task to be interrupted by higher priority tasks that do not need the resource. Because this preemption can occur arbitrarily deep, the priority inversion is said to be unbounded. It is impossible to avoid at least one level of priority inversion in multitasking systems that must share resources, but one would like to at least bound the level of inversion. This problem is addressed by the priority ceiling pattern. The basic idea of the priority ceiling pattern is that each resource has an attribute called its priority ceiling. The value of this attribute is the highest priority of any task that could ever use that particular resource. The active objects have two related attributes: nominal priority and current priority. The nominal priority is the normal executing priority of the task. The object's current priority is changed to the priority ceiling of a resource it has currently locked as long as the latter is higher.

3.3.3 Dynamic Priority System: Dynamic priority systems assign task priority at run-time based on one of several possible strategies. The three most common dynamic priority strategies are:

- 1. Earliest Deadline First

- 2. Least Laxity

- 3. Maximum Urgency First

In Earliest Deadline First (EDF) scheduling, tasks are selected for execution based on which has the closest deadline. This algorithm is said to be *dynamic* because task scheduling cannot be determined at design time, but only when the system runs. In this algorithm, a set of tasks is schedulable if the sum of the task loadings is less than 100%. This algorithm is optimal in the sense that if it is schedulable by other algorithms, then it is also schedulable by EDF. However, EDF is not stable; if the total task load rises above 100%, then at least one task will miss its deadline, and it is not possible to predict in general which task will fail. This algorithm requires

additional run-time overhead because the scheduler must check all waiting tasks for their next deadline frequently. In addition, there are no formal methods to prove schedulability before the system is implemented.

Laxity for a task is defined as the time to deadline minus the task execution time remaining. Clearly, a task with a negative laxity has already missed its deadline. The algorithm schedules tasks in ascending order of their laxity. The difficulty is that during run-time, the system must know expected execution time and also track total time a task has been executing in order to compute its laxity. While this is not conceptually difficult, it means that designers and implementers must identify the deadlines and execution times for the tasks and update the information for the scheduler every time they modify the system. In a system with hard and soft deadlines, the Least Laxity (LL) algorithm must be merged with another so that hard deadlines can be met at the expense of tasks that must meet average response time requirements (see MUF, below). LL has the same disadvantages as the EDF algorithm: it is not stable; it adds run-time overhead over what is required for static scheduling, and schedulability of tasks cannot be proven formally.

Maximum Urgency First (MUF) scheduling is a hybrid of RMS and LL. Tasks are initially ordered by period, as in RMS. An additional binary task parameter, criticality, is added. The first n tasks of high criticality that load under 100% become the critical task set. It is this set to which the Least Laxity Scheduling is applied. Only if no critical tasks are waiting to run are tasks from the noncritical task set scheduled. Because MUF has a critical set based on RMS, it can be structured so that no critical tasks will fail to meet their deadlines.

### IV. PATTERNS

With this background of various scheduling approaches in Real-Time Systems, we can now suggest suitable patterns known as Execution Control Patterns for scheduling tasks. They deal with the policy by which tasks are executed in a multitasking system. This is normally executed by the Real-Time Operating System, if present. Most Real-Time Operating Systems offer a variety of scheduling options. The most important of these are listed here as execution control patterns [3].

- 1. Cyclic Executive Pattern for simple task scheduling.

- 2. Time Slicing Round Robin Pattern fairness in task scheduling.

- 3. Static Priority Pattern preemptive multitasking for schedulable systems.

- 4. Semi-static priority Priority Ceiling Pattern.

- 5. Dynamic Priority Pattern preemptive multitasking for complex systems.

The primary difference occurs in the policy used for the selection of the currently executing task.

### 4.1 Cyclic Executive Pattern

In the cyclic executive pattern the kernel (commonly called the *executive* in this case) executes the tasks in a

prescribed sequence. Cyclic executives have the advantage that they are "brain-dead" simple to implement and are particularly effective for simple repetitive tasking problems. Also, it can be written to run in highly memory-constrained systems where a full RTOS may not be an option. However, they are not efficient for systems that must react to asynchronous events and not optimal in their use of time. There have been well-publicized cases of systems that could not be scheduled with a cyclic executive but were successfully scheduled using preemptive scheduling. Another disadvantage of the cyclic executive pattern is that any change in the executive time of any task usually requires a substantial tuning effort to optimize the timeliness of responses. Furthermore, if the system slips its schedule, there is no guarantee or control over which task will miss its deadline preferentially.

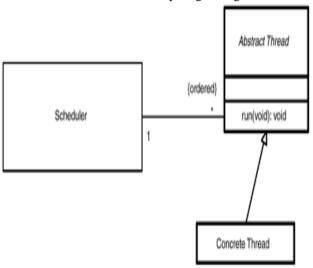

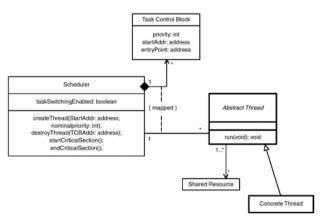

Figure 1.[4] shows how simple this pattern is. The set of threads is maintained as an ordered list (indicated by the constraint on the association end attached to the *Abstract Thread* class). The Cyclic Executive merely executes the threads in turn and then restarts at the beginning when done. When the Scheduler starts, it must instantiate *all* the tasks before cycling through them.

Figure 1.Cyclic Executive Pattern

### 4.2 Time Slicing – Round Robin Pattern

The kernel in the time slicing pattern executes each task in a round-robin fashion, giving each task a specific period of time in which to run. When the task's time budget for the cycle is exhausted, the task is preempted and the next task in the queue is started. Time slicing has the same advantages of the cyclic executive but is more time based. Thus it becomes simpler to ensure that periodic tasks are handled in a timely fashion. However, this pattern also suffers from similar problems as the cyclic executive. Additionally, the time slicing pattern doesn't "scale up" to large numbers of tasks well because the slice for each task becomes proportionally smaller as tasks are added.

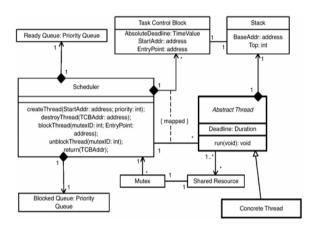

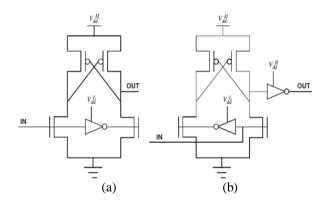

The Round Robin Pattern is a simple variation of the Cyclic Executive Pattern. The difference is that the *Scheduler* has the ability to preempt running tasks and

does so when it receives a tick message from its associated *Timer*. Two forms of the Round Robin Pattern are shown below. The complete form (Figure 2a [4]) shows the infrastructure classes *Task Control Block* and *Stack*. The simplified form (Figure 2b [4]) omits these classes.

Task Control Block

Stack

Figure 2. Round Robin Pattern

### 4.3 Static Priority Pattern

In a static system, a task's priority is determined at compile time and is not changed during execution. This has the advantages of simplicity of implementation and simplicity of analysis.

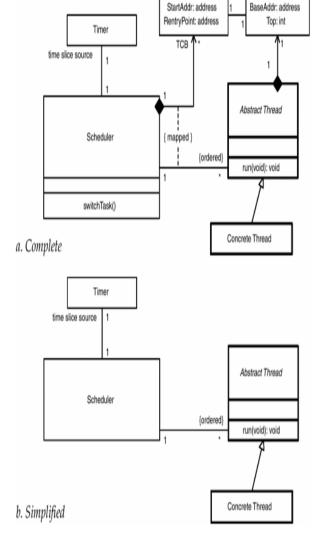

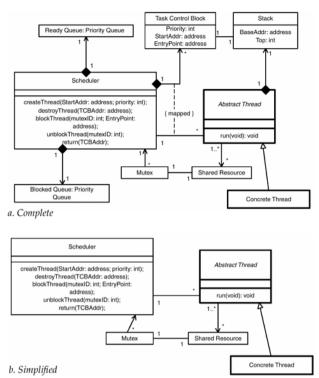

Figure 3. [4] shows the basic structure of the pattern. Each «active» object (called *Concrete Thread* in the figure) registers with the *Scheduler* object in the operating system by calling *createThread* operation and passing to it, the address of a method defined. Each *Concrete Thread* executes until it completes (which it signals to the OS by calling *Scheduler::return()*), it is preempted by a higher-priority task being inserted into the *Ready Queue*, or it is blocked in an attempt to access a *Shared Resource* that has a locked *Mutex* semaphore.

Figure 3. Static Priority Pattern

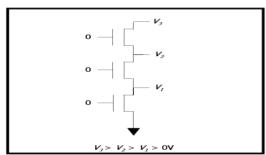

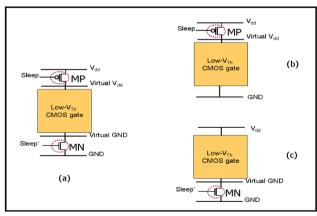

### 4.4 Semi-static Priority - Priority Ceiling Pattern

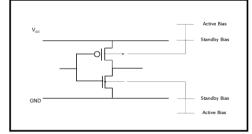

The Priority Ceiling Pattern, or Priority Ceiling Protocol (PCP) as it is sometimes called, addresses both issues of bounding priority inversion (and hence bounding blocking time) and removal of deadlock. It is a relatively sophisticated approach, more complex than the previous methods. It is not as widely supported by commercial RTOSs, however, and so its implementation often requires writing extensions to the RTOS. Figure 4. [4] shows the Priority Ceiling Pattern structure.

Figure 4. Priority Ceiling Pattern

### 4.5 Dynamic Priority Pattern

The Dynamic Priority Pattern is similar to the Static Priority Pattern except that the former automatically updates the priority of tasks as they run to reflect changing conditions. There are a large number of possible strategies to change the task priority dynamically. The most common is called *Earliest Deadline First*, in which

the highest-priority task is the one with the nearest deadline. The Dynamic Priority Pattern explicitly emphasizes *urgency* over *criticality*.

Figure 5.[4] shows the Dynamic Priority pattern structure.

Figure 5. Dynamic Priority Pattern

### V. TOOL SUPPORT

It is proposed to develop a GUI based tool, which will help the users in selecting appropriate scheduling strategy depending upon the nature and parameters of the real-time tasks in the application being developed. The tool will educate the users about merits and demerits of each scheduling strategy and help in identifying appropriate design pattern. Further, the tool will also generate the code for the chosen design pattern in real-time java. Thus, the design and development activities may be completed in less time and with more accuracy, as the code is generated automatically.

### Conclusions

In this paper, we have reviewed and summarized various scheduling approaches for real-time systems. Further, we have listed suitable design patterns for these varied scheduling strategies. The proposed tool to generate code for a chosen design pattern will greatly help the developer in reducing development effort, reducing development time and provides ready-made code, which can be plugged into the developer's application.

### REFERENCES

- [1] Gamma, Erich, Richard Helm, Ralph Johnson, and John Vlissides. *Design Patterns: Elements of Reusable Object-Oriented Software*. Reading, MA: Addison-Wesley, 1995.

- [2] Jane W.S. Liu, *Real-Time Systems*, Pearson Education 2006.

- [3] Bruce Powel Douglass, White Paper on Real-Time Design Patterns 1998

- [4] Bruce Powel Douglass Real-Time Design Patterns: Robust Scalable Architecture for Real-Time Systems, Addison Wesley 2002

- [5] Stankovic, J., M. Spuri, K. Ramamritham, and G. Buttazzo. *Deadline Scheduling for Real-Time Systems*, Norwell, MA: Kluwer Academic Press, 1998.

- [6] Douglass, Bruce Powel. *Doing Hard Time: Developing Real-Time Systems with UML, Objects, Frameworks, and Patterns*, Reading, MA: Addison-Wesley, 1999.

- [7] A System of Patterns: Pattern-Oriented Software Architecture Buschmann, et. al., John Wiley & Sons, 1996.

# Architecture Of Intelligent Process Controlling Model Through Image Mining

Dr.Hari Ramakrishna

Chaitanya Bharathi Institute of Technology, Department of CSE, Hyderabad, A.P., India Email: dr.hariramakrishna@rediffmail.com

Abstract—In this paper, research potentials and challenges raised through visual data mining and image mining are presented. Various views of visual data mining and a new vision of visual data mining and its applications are discussed. A case study of an application of visual data and image mining for improving quality processes of an educational organization is presented. Various research challenges raised by such image mining applications are described.

Index Terms— Knowledge acquisition, Visual Data mining, Data Mining, Image Mining, Real time data mining, Architectural framework, Process Controller.

### I. INTRODUCTION

An image is equal to thousands of words. It is possible to present complex data in a predefined format of an image. For Example, Software engineering domain uses UML which represents its models in the form of a set of diagrams. These UML diagrams has particular schema and defines a set of rules for designing. These UML Models holds lot of information with semantic meaning. A software developer can get required information along with complex logic of system from these UML diagrams.

Similarly, most of the images represent lot of data without following a particular pattern or rule. Extracting information and patterns from the data available in an image or a set of images can be referred as Image mining. A satellite Image holds lot of information in an unprocessed form. Many researchers are using Data Mining Algorithms for extract information and knowledge from satellite images [4].

A Human Expert gains knowledge from the images captured through his vision applying natural data mining algorithms running in his mind known as human intelligence. This enables a human expert to control set of quality processes of any domain of his expertise. A robot can mimic exactly like a human expert if it is charged with powerful Image mining algorithms through an intelligent software framework.

This paper presents model application framework using Visual Data mining and image mining for improving quality of processes of an organization through visual aids and intelligent software model. A case study of controlling educational processes through visual data and image mining is discussed in this paper.

### II. VISUAL DATA MINING VS VISUAL DATA

The term Visual Data mining is defined differently depending on its usage at deferent application. The Data Mining defined visual data mining as a tool to represent graphical data for taking decisions. It is used to represent complex data sets or patterns in a graphical form for taking decisions. Though it proves that a graph or an image can be used to generate knowledge from complex data sets, it is limiting the word only to the extent of generating set of mathematical graphs. This paper uses the word for extracting information and knowledge from real time images generated through visual aids for taking decisions.

Visual data plays a major role in knowledge extraction. Educational experts suggest visual tools (Visual Aids) as better process for knowledge acquisition and better communication even for a human expert. The word Visual data mining should be redefined for better use as set of algorithms models which extract data from images collected using visual aids for acquiring required knowledge for taking decisions. The term visual aid refers to human eye, a Video or digital Camera or a satellite. A human Expert extracts Knowledge for taking decisions through his sight applying natural Visual data and image mining algorithms functioning in this mind.

Applying such concepts enables a computer based system to take decisions through extracting knowledge from images collected from digital device. The final objective of such models is to charge the robots with powerful knowledge acquisition algorithms to mimic like a human expert collecting data from visual devices (multimedia devices).

# III. A CASE STUDY OF INTELLIGENT PROCESS CONTROLLER EDUCATIONAL ORGANIZATION

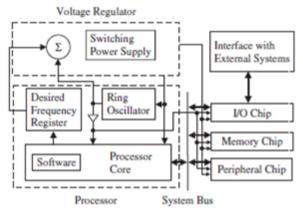

### A. E-College System

The E-college Product is a Web based Software Model which automates the processes of a huge educational organization. General objective of any educational environment is to control the educational processes to produce the best professionals to the society. Several methodologies are available to improve the educational process with the help of Information Technology. E-College is a Computer based system which implements processes of a Huge Educational organization for improving the quality of the educational system.

## B. Architectural of intelligent process control model for ECollege

The major challenge of educational process is to monitor the academic processes. For example consider the process of monitoring the attendance of the students in the class rooms. This will be managed with attendance registers. All the registers data can be made available over internet either adding the data from the registers or by automatically collecting from finger-prints of the students from the class rooms. This will not provide authenticated information for the following questions:

- 1. Whether all students are present throughout the class?

- 2. When the class started? What will be the strength of the class at the beginning and at the end?

- 3. Any malpractice took place in giving the attendance?

The solutions for all the questions will be by appointing an agent or an academic controller who will be observing the classes on line. This can be done even by keeping the digital cameras in the class and observing them. Such process has the following disadvantages:

- 1. The data is not persisted?

- Very difficult for a human controller to monitor if the number of classes are large and the class schedules (or time tables) are complex.

The solutions for such processes are addressed by a simple intelligent software model. This model controls the classes with the visual aids. The computer module can manage complex class schedules and huge data. In the computer modules can collect visual pictures from required classes and extract data and make them persistent. This enable the module to evaluate the regularity of the class room lectures.

This model is replacing a *Dean Academics* who monitors the class rooms functioning with Software Module capable of collecting real time data from the class rooms using simple digital cameras and a software model.

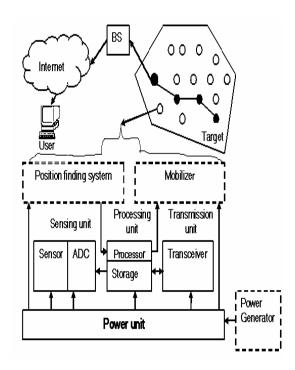

### IV. CLASS ROOM MONITOR ARCHITECTURE

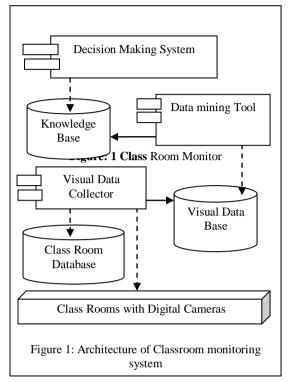

Architecture of the Class *Room Monitor* is presented in the following Figure 1.

In this model class rooms are equipped with digital cameras. The class room database consists of information related to class room sessions. The visual data collector will collect the information in visual form with the help of digital cameras based on class room schedule databases. This will extract required information from visual data and builds suitable data base with collected visuals. Typical data mining algorithms are applied for building Knowledgebase. The knowledge base is used to extract required information for decision making.

Such systems can be used to measure regularity of the class room lectures, regularity of students attending the class and regularity of the faculty. This system works like an *automated real time software dean academics* for monitoring the class room lectures. Similar models can be developed for several such applications for monitoring

the processes of organizations for improving the performance.

Picture are collected depending on class schedules and prescribed frequencies. For example if a class start at 9am and duration is one hour we can set system such that it collect pictures at 9.00 9.15 and 9.30 and 945 and 10.00 and 10.15. This will enable expert providing the following answers.

- 1. When the class started? How many students at the beginning of the class?

- 2. When all students are present in class?

- 3. When the class ended? How many students are present at the end of class?

- 4. Whether the class ended at time or not?

Digital devices can be configures to take pictures depending on time or on events as per the need of the system. This logic can be extended to other multimedia devices such as audio or video devices.

Such systems need software facilities to update changes in the timetables at run time which enable to change the class room or to change teacher, in order to make the visual devices act accordingly.

### V. IMAGE MINING REQUIREMENTS

This model identifies and raises requirements from image mining which enforse the human expert to interfear for automatic decition making. In this model a human expert is neded to identify the number of students in the class room from the picture collected and stored in database. Image mining algorithom which collect number of students in a class from the picture makes the software model totally automated. An alogorithm to

recorgnize a student from a picture with total confidence will enable the software to generate automated attendence register with a simple picture collected.[1,2,3,5,7]

### V. OTHER APPLICATIONS

We can find several applications which are useful for rural development. Farmers who involve in cultivation need advice on their crops at frequent intervals of time. Similar software model which collects images as per the requirement can be used for advising the farmers. Like medical image mining algorithms which recognize medical problems if algorithms are generated for finding problems from villages can be benefited through these models. [8] At present similar software models are available but not fully automated. Fully automated models decrease human expert time and provide fast decisions which are required for providing immediate solutions for the problem. This will enable to use such applications even for *Disaster Management*.

Several similar applications based on image mining are in use. For example *Traffic Control system* of several contrives take pictures of vehicles which violate the traffic rule. They have the intelligence of recognizing the number automatically from the picture and collect the details of the owner and vehicle from online database. Such systems have the capability of automatically recording the defaulters. [6]

Similar other application is for the payment of the bills from the scanned hard copy of the bill. The image mining algorithm can recognize the validity of the bill along with bill number, customer details and amount payment details. The percentage of the accuracy of the information collected from these image mining algorithms changes with risk rate of the applications.

### **CONCLUSIONS**

This paper identifies the need to develop the intelligent software models for improving the organizational processes through data mining techniques. It also indentifies the need in the domain of image mining which supports such processes for total automation. The paper identified the use of the multimedia devices and data mining algorithms to extract information through them to enable software models to mimic like human experts through total automation of the software. This paper identified the need for redefining the visual data mining from 'providing visual tools to human expert for taking decisions' to "extracting information from visuals" for total automation.

### ACKNOWLEDGMENT

The authors wish to thank faculty of computer science and engineering department of CBIT who are doing research in Image processing and data mining for their suggestions and for participating in the discussions.

#### REFERENCES

- G. Kukharev and E. Kamenskaya, "Application of two-dimensional canonical correlation analysis for face image processing and recognition", Pattern Recognition and Image Analysis, Volume 20, Number 2 june 2010.

- [2] N. ALUGUPALLY, A. SAMAL, D. MARX AND S. BHATIA, "ANALYSIS OF LANDMARKS IN RECOGNITION OF FACE EXPRESSIONS "Pattern Recognition and Image Analysis, Volume 21, Number 4 December 2011.

- [3] Araujo A., Bellon O., Silva L., Vieira E., Cat M. "Applying Image Mining to Support Gestational Age Determination" The Insight Journal, June 30, 2006, presented at MICCAI Open Science Workshop.

- [4] "An Useful Information Extraction using Image Mining Techniques from Remotely Sensed Image" Dr.C.Jothi Venkateswaran et al. / (IJCSE) International Journal on Computer Science and Engineering Vol. 02, No. 08, 2010, 2577-2580.

- [5] Hilliges O., Kunath P., Pryakhin A., Butz A., Kriegel H.-P.: "Browsing and Sorting Digital Pictures using Automatic Image Classification and Quality Analysis", Proc. 12th Int. Conf. on Human-Computer Interaction (HCII'07), Beijing, China, 2007, in: LNCS, Vol. 4552, 2007, pp. 882-891.

- [6] Kriegel H.-P., Kunath P., Pfeifle M., Renz M.: ViEWNet: "Visual Exploration of Region-Wide Traffic Networks", Proc. 22nd Int. Conf. on Data Engineering (ICDE 2006), Atlanta, GA, 2006, paper no. 166.

- [7] Multimedia Data Mining (MDM/KDD'03), Washington, DC, 2003, pp. 64-71.

- [8] "E-Sagu: An IT based Personalized Agro-Advisory System "A Project of Media Lab AsiaExecuted by IIIT, Hyderabad and Media Lab Asia in association with Nokia, http://www.esagu.in.

# Pattern Methodology Of Documenting And Communicating Domain Specific Knowledge

Dr.Hari Ramakrishna<sup>1</sup> and Dr.K.V Chalapathi Rao<sup>2</sup>

<sup>1</sup>Chaitanya Bharathi Institute of Technology, Department of CSE, Hyderabad, A.P., India

Email: dr.hariramakrishna@rediffmail.com

<sup>2</sup>CVR College of Engineering, Department of CSE, Ibrahimpatan, R.R.District, A.P., India

Email: chalapatiraokv@gmail.com

Abstract— the main objective of this paper is to present pattern methodology of documenting and communicating domain specific knowledge along with a brief historic review of the domain. This paper presents pattern methodology of documenting domain specific knowledge along with few simple framework samples.

Index Terms—pattern, pattern language, frameworks, pattern frames, Graphic frameworks.

### I. INTRODUCTION

Patterns for software development are one of the latest trends to emerge from the object oriented approach. Fundamental to any science or engineering discipline is a common vocabulary for expressing its concepts, and a language for expressing these interrelationships. The goal of patterns within the software community is to create a body of literature to help software developers resolve recurring problems encountered throughout all of software development. Patterns help create a shared language for communicating insight and experience about these problems and their solutions.

The current use of the term *pattern* is derived from the writings of the architect *Christopher Alexander* who has written several books on the topic as it relates to urban planning and building architecture. Although these books are ostensibly about architecture and urban planning, they are applicable to many other disciplines, including software development.

Alexander proposes a paradigm for architecture based on three concepts namely Quality, Gate and the Way. Quality is freedom, wholeness, completeness, comfort, harmony, habitability, durability, openness, resilience, variability and adaptability. The gate is the mechanism that allows us to reach the quality. And the Way is progressively evolving an initial architecture, which then flourishes into a live design possessing the quality. [1]

In 1987 Ward Cunningham and Kent Beck were working with Smalltalk and designed user interfaces. They decided to use some of Alexander's ideas to develop a small five-pattern language for guiding novice Smalltalk programmers. They presented the results at OOPSLA-87 in Orlando in the paper "Using Patterns Language for Object-Oriented Programming". Soon after, Jim Coplien (referred to as Cope) began compiling a catalog of C++ idioms. These are one kind of patterns. Later they are published as "Advanced C++ Programming Styles and Idioms". [2]

From 1990 to 1992 the members of GOF (Erich Gamma, Richard Helm, Ralph Johnson and John Glissades frequently referred as *GOF* Gang of Four) had done some work compiling a catalog of patterns. Discussions of patterns abounded at OOPSLA-91 workshop conducted by *Bruce Andersen*. This was repeated in 1992. Many pattern domain experts participated in these workshops including *Jim Coplien*, *Doug Lea, Desmond D'Souza,Norm Kerth*, *Wolfgang Pree* and others.

In August 1993, *Kent Beck* and *Grady Booch* sponsored a mountain retreat in *Colorado*, the first meeting of what is now known as the *Hillside Group*. Another pattern workshop was held at OOPSLA –93 and then in April of 1994, the Hillside Group met again to plan the first conference on Patterns Languages for Program Design (referred as PloP or PloPD). Shortly thereafter the GOF released a book on Design Patterns [3]. Most of the patterns presented in that book are from Erich's Ph.D thesis. Several conferences are continuously organized on this domain.

Software patterns first became popular with the wide acceptance of the book 'Design Patterns: Elements of Reusable Object-Oriented Software'. Patterns have been used for many different domains ranging from organizations and processes to teaching and architecture. At present the software community is using patterns largely for software architecture, design, development processes and organizations. Though several conference proceedings and books are available on this domain, other books that helped popularize patterns are 'Pattern-Oriented Software Architecture: A system of Patterns (also called as POSA book) by Frank Buschmann, Regine Meunier, Hans Rohnert, Peter Sommerlad, and Michael Stal ( referred as Gang of Five GoV ). Collection of selected papers from the first and second conferences on Patterns Languages for Program Design is released as a book namely "Pattern Languages of Program Design".

At present Patterns are adopted into application domains for example: [4].

- Patterns in software development generally, including software design, software engineering, and software architecture

- ii) Process patterns for management and development processes

- iii) Patterns for human-computer interaction (user-interface patterns, or novel modes of interaction)

- iv) Patterns for education (ranging from professional training to classroom teaching)

- v) Patterns for business and organizations

- vi) Modeling patterns, analysis patterns, design patterns

- vii) Patterns for object-oriented design, aspectoriented design, and software design generally

- viii)Patterns to describe libraries, frameworks, and other reusable software elements

- ix) Patterns for middleware, including distribution, optimization, security, and performance improvement

- x) Domain specific patterns and technology specific patterns, as well as generic patterns

- xi) Patterns for refactoring and reengineering

- xii) Formal models and type systems for patterns

- xiii) Programming environments, software repositories, and programming languages for patterns

- xiv) The use of patterns to improve quality attributes such as adaptability, evolvability, reusability and cost-effectiveness

### II. PATTERNS AND PATTERN LANGUAGES

Pattern can be defined as "Reusable solution for recurring problem". Patterns Dirk Riehle and Heinz Zullighoven define pattern as, "the Abstraction from a concrete form, which keeps recurring in specific nonarbitrary contexts". Another definition of pattern for software community is given as, "a named nugget of insight that conveys the essence of a proven solution to a recurring problem within a certain context amidst competing concerns".

Each pattern is a three-part rule, which expresses a relation between a certain context, and a certain system of forces, which occurs repeatedly in that context, and a certain software configuration, which allows these forces to resolve themselves. Alexander defines three-part rule, as "Each pattern is a three-part rule, which expresses a relation between a certain context, a problem and a solution."

Cope says that a good pattern does the following:

- 1) It solves a Problem

- 2) It is a proven concept

- 3) The solution is not obvious

- 4) It describes a relationship

- 5) The pattern has a significant human component (like comfort, quality of life)

If something is not a pattern, it doesn't mean that it is not good. Similarly if it is a pattern, hopefully it is good but need not be always. Many of the initial patterns focused in the software community are design patterns. The patterns in the GOF book are Object Oriented Design Patterns [3]. There are many other kinds of software patterns beside design patterns, analysis *patterns* published by Marin Fowler and other patterns like *organizational patterns* are also available.

Architectural patterns express a fundamental structural organization or schema for software systems. Design Patterns provide a schema for refining the subsystems or

components of a software system or the relationships between them. They describe commonly recurring structure of communicating components that solve a general design problem within a particular context.

Idioms are low-level patterns specific to a programming language. An idiom describes how to implement particular aspects of component or the relationship between them using the features of the given language. The difference between these patterns is in their corresponding level of abstraction.

*Riehle and Zullighoven* have classified patterns as Conceptual patterns, Design Patterns and Programming Patterns [12].

A collection of patterns forms a vocabulary for understanding and communicating ideas. A pattern language is such collection skillfully woven together into a cohesive "whole" that reveals the inherent structure and relationships of its constituent parts towards fulfilling a shared objective [1]. If a pattern is a recurring solution to a problem in a context given by some forces, then a pattern language is a collection of such solutions, which at every level of scale, work together to resolve a complex problem into an orderly solution according to a predefined goal.

Cope defines a pattern language as a collection of patterns and the rules to combine them into an architectural style. Pattern languages describe software frameworks or families of related systems [5, 6, and 7]. In some other context, Cope defines pattern language as a structured collection of patterns that build on each other to transform needs and constraints into architecture.

### III. DOMAIN SPECIFIC PATTERN LANGUAGES

The following is a description of view on domain specific patterns and pattern languages as per the domain experts.

The domain-specific patterns are confidential —they represent a company's knowledge and expertise about how to build particular kinds of applications; so references to them are not generally available. One can however more and more of this knowledge will become public over time. In the long run, sharing experience is usually more effective for everyone than trying to hold onto secrets.

The development of complete pattern language is an optimistic but worthwhile goal. Such a language provides solutions to all design problems that can occur in the respective domains. Christopher Alexander claims to have done this in the domain of *Architecture*. Pattern language already exists for small sub-domains of software design, for example the CHECKS pattern language for information integrity [8].

It would be very beneficial to have a pattern language that covers a substantial part of the design space of the respective domains.

### IV. FRAMEWORKS

The software frameworks are closely related to design patterns and object-orientation. A software framework is

a reusable mini-architecture that provides the generic structure and behavior for a family of software abstractions, along with a context of mimes/metaphors that specify their collaboration and use within a given domain. The following presents views of Brad Appleton on frameworks.

The framework accomplishes patterns by hard coding the context into a kind of "virtual machine" (or "virtual engine"), while making the abstractions open-ended by designing them with specific *plug-points* (also called *hot* spots). These plug-points (typically implemented using callbacks, polymorphism, or delegation) enable the framework to be adapted and extended to fit varying needs, and to be successfully combined with other frameworks. A framework is usually not a complete application: it often lacks the necessary applicationspecific functionality. Instead, an application may be constructed from one or more frameworks by inserting this missing functionality into the plug-and-play "outlets" provided by the frameworks. Thus, a framework supplies the infrastructure and mechanisms that execute a policy for interaction between abstract components with open implementations [9].

The GOF also defines object-oriented frameworks as: "a set of cooperating classes that makeup a reusable design for a specific class of software". A framework provides architectural guidance by partitioning the design into abstract classes and defining their responsibilities and collaborations. A developer customizes a framework to a particular application by sub classing and composing instances of framework classes. For example Microsoft Application framework belongs to this kind.

A framework dictates the architecture of the application. It will define the overall structure, such as partitioning into classes and objects, the key responsibilities, how the classes and objects collaborate, and the thread of control

A framework predefines these design parameters so that the application designer/implementer can concentrate on the specifics of the application. The framework captures the design decisions that are common to its application domain. Frameworks thus emphasize *design reuse* rather than code reuse, though a framework will usually includes concrete subclasses that work directly.

The difference between a framework and an ordinary programming library is that a framework employs an *inverted flow of control* between itself and its clients. When using a framework, one usually just implements a few callback functions, or a few specialized classes, and then invokes a single method or procedure. At this point, the framework does the rest of the work, invoking any necessary client callbacks or methods at the appropriate time and place. For this reason, frameworks are often said to abide by the Hollywood Principle "Don't call us, we'll call you." or the Greyhound Principle "Leave the driving to us."

Design patterns may be employed both in the design and the documentation of a framework. A single framework typically encompasses several design patterns. In fact, a framework can be viewed as the implementation of a system of design patterns. Despite the fact that they are related in this manner, it is important to recognize that frameworks and design patterns are two distinctly separate entities: a framework *is executable software*, whereas design patterns represent knowledge and experience *about software*. In this respect, frameworks are of a physical nature, while patterns are of a logical nature: frameworks are the *physical realization* of one or more software pattern solutions; patterns are the instructions for *how to implement* those solutions.

The major differences between design patterns and frameworks are as follows: [3].

Design patterns are more abstract than frameworks. Frameworks can be embodied in code, but only examples of patterns can be embodied in code. Strength of frameworks is that they can be written down in programming languages and not only studied but executed and reused directly. In contrast, design patterns have to be implemented each time they are used. Design patterns also explain the intent, trade-offs, and consequences of a design.

Design patterns are smaller architectural elements than frameworks. A typical framework contains several design patterns. The reverse is never true, but one can build patterns for frameworks. Several domain specific patterns are available for designing frameworks. [10]. The San Francisco Frameworks are example of popular frameworks available in the software market [11].

### V. Frameworks Samples

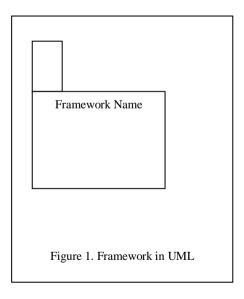

Typical framework samples starting from representation of a framework in UML, Figure 1 presents the UML building block for representing a framework.

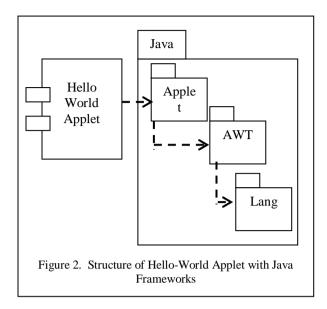

A simple hello world program in Java uses java framework. This example can be implemented using java Applet. The Java Applet is a part of Java Framework. This in turn depends on AWT and Java language. The following Figure 2 represents a hello world Applet component structure in UML using Java frameworks.

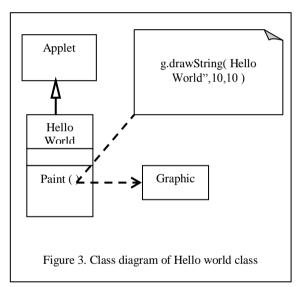

From this diagram, it can be observed that Helloworld applet is depending on Java Applet. The HTML client or Java frame which includes the Hello-World Applet gets Hello-World Interface through the Java Applet. Message from client application will invoke the Java Applet that in turn sends them to the Hello-world Applet. For displaying the hello world message the Hello-world applet implementation again depends on Java graphic library. The class diagram of the hello world example is displayed in the following Figure.3

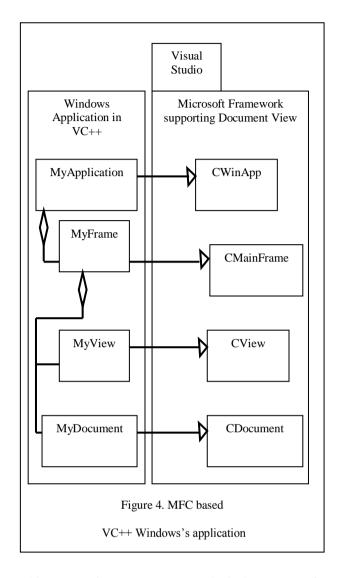

The following application which uses application wizard of Microsoft demonstrates a better view of anther framework. This application depends and reuses Microsoft Document View Architecture. Microsoft provides Application Wizard for using the framework and class wizard for managing the applications. A simple MFC based application structure in UML is presented in the following Figure 4.

This UML Diagram represents a logical structure of Document View Architecture. The application class of the client module is inherited from CWinApp, a class of Microsoft MFC framework. In fact the Application wizard will decide from which class of CWinApp class group the MyApplication class should be inherited, depending on the requirement of the client specified through application wizard. The user requirements are collected in six steps at the time of creating an application (project workspace) in VC++ through application wizard. The type of project workspace also will change the aggregation-combination, depending on how the user is exporting his functionality.

The ATL technology of Microsoft also provides similar frameworks for supporting Automation layer; component technology and web based computing. Several commercial frameworks available in the market use Microsoft frameworks. These frameworks are referred to as Middleware integration frameworks.[10] Microsoft Visual studio present frameworks for providing web services and other features. These enable the client to use the latest technology without having detailed

knowledge of the hidden technology. Such frameworks enable common use to use complex technology.

Benefits of Object Oriented Application Frameworks are Modularity, Reusability, Extensibility, and Inversion of control. Some of the Challenges of Object Oriented Application Frameworks are Development efforts, Learning curve, Integratability, Maintainability, Validation and defect removal.

### VI. OBJECT ORIENTED GRAPHIC FRAMEWORKS

Several pattern languages are available for handling the problems and for documenting and communicating the skill set of a Graphic and CAD developer. A simple graphic framework known as pattern-frame for integrating existing graphic libraries with Microsoft ATL framework is presented briefly as an example.

*Name*: Middleware integration pattern-frames

*Intent*: To export object oriented framework into component oriented framework using middleware frameworks.

Motivation and Applicability: The object oriented graphic frameworks require to be ported into new technology component-oriented technology for providing better interfaces to the client.

In this *pattern frame*, the object oriented frameworks is ported into component-oriented frameworks through integrating middleware frameworks for supporting component technology.

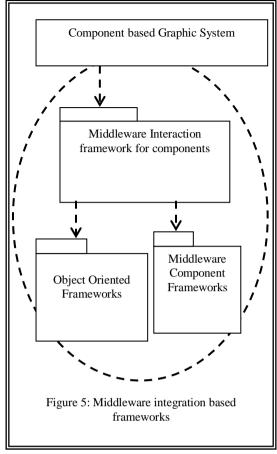

*Structure*: The structure of these frameworks is presented in the following UML diagram presented in the Figure 5.

Participants and collaboration: Figure 5. presents mainly three participants.

- The object oriented frameworks: They are some

of the object oriented frameworks, which need

to be ported to component technology. In this

example a three dimensional object oriented

graphic framework with all user required

graphic functionality (domain specific

functionality) is selected for porting in to COM

technology.

- 2. The Middleware Integration frameworks: These frameworks defines interface for exporting the functionality of object oriented framework and aggregate the object oriented frameworks to form black box. They will depend on Middleware component frameworks like Microsoft ATL, and Java beans frameworks. They basically provide automation layer. Few VB command are presented in table 1.

- The Middleware component framework: This is a framework used to build components, supporting component technology. Examples of middleware component frameworks are Java Beans development kit, Microsoft Active Template Libraries.

### A. Implementation and Code:

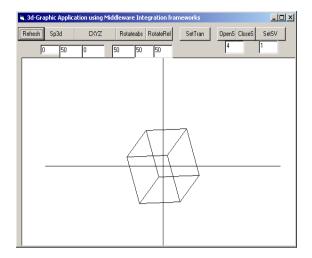

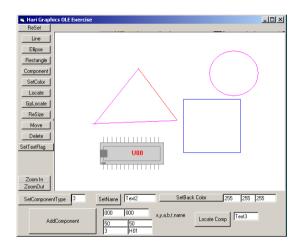

The selected object oriented graphic framework can be exported to VB client using Active X controls. Building a graphic component is possible by integrating traditional graphic framework with Active X controls, which is a middleware framework. This will export traditional graphic framework functionality to VB client. Table1 shows sample VB front-end application commands used to control the graphic component frameworks. Sample view of the e VB application is presented in the Figure 6. HGP3D1 is the name of the framework component.

Table I.

Few VB Statements used in the application

HGP3D1.Sp3d Text1.Text, Text2.Text, Text3.Text, Text4.Text

HGP3D1.RoteteSegmentAbs Text7.Text, Text4.Text, Text5.Text, Text6.Text

HGP3D1.ShowAll

HGP3D1.CloseSegment Text7.Text

HGP3D1.RotateSegRel Text7.Text, Text4.Text, Text5.Text, Text6.Text

Figure: 6 A Three Dimensional graphic Framework A sample output of the application used to simulate PCB board using same framework is presented in the following Figure 7.

Figure 7. A graphic Frameworks for simulating PCB

Several framework patterns for the development of Graphic frameworks are presented in the following section.

# VI. PATTERN LANGUAGE FOR GRAPHIC FRAMEWORK

Problems in evolving Graphic frameworks can be documented adapting pattern approach for provide solutions. Sixteen typical common design and implementation issues are identified and they are classified into three groups depending on nature of the issues namely *object oriented*, *component oriented* and *distributed & web based pattern frames*. The following are a catalog of few pattern frames [10].

### A. Object Oriented pattern Frames

These are based on simple object oriented patterns. They make lightweight frameworks. They provide solutions for under engineering problems for developing frameworks.

Table II.

Object Oriented Pattern Frames

| Name                                 | Intent                                                                                    |

|--------------------------------------|-------------------------------------------------------------------------------------------|

| TRADITIONAL<br>GRAPHIC<br>FRAMEWORKS | This will apply traditional graphic techniques for building frameworks                    |

| FUNCTION CLASS<br>FRAMEWORKS         | This will apply basic object oriented patterns for building configurable function classes |

| FOUNDATION CLASS<br>FRAMEWORKS       | This will provide hot spot object libraries for reusing most common modules of the domain |

| WHITE -BOX<br>FRAMEWORKS             | This will generate object library for configurable generic domain specific classes        |

| FLYWEIGHT OBJECT<br>FRAMEWORKS       | This will decrease number of classes and number of objects in a system                    |

### B. Component Oriented Pattern Frames

These frameworks are based on Component technology. All are black box frameworks. They provide solutions for building Component based application frameworks.

Table III.

Component Oriented Pattern Frames

| Name                                             | Intent                                                                                            |  |  |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------|--|--|

| MIDDLEWARE<br>INTEGRATION<br>BASED<br>FRAMEWORKS | This will reuse middleware integration frameworks for building Enterprise frameworks              |  |  |

| Component based frameworks                       | This will apply patterns defined on components for providing black box frameworks                 |  |  |

| Abstract<br>Component<br>frameworks              | This will generate black box framework components using simple object oriented primitive patterns |  |  |

| Component wrapper frameworks                     | This will apply simple object oriented primitive patterns for using black box frameworks          |  |  |

### C. Distributed nad Webbased Pattern Frames

These are useful for building frameworks for supporting typical distributed and web based application requirements.

Table IV.

Distributed Web based Pattern Frames

| Name                      | Intent                                                                                        |  |  |  |

|---------------------------|-----------------------------------------------------------------------------------------------|--|--|--|

| DISTRIBUTED<br>FRAMEWORKS | This will provide environment for building domain specific distributed application components |  |  |  |

| WEB ENABLED<br>FRAMEWORKS | This will provide environment for building web enabled applications                           |  |  |  |

| WEB BASED<br>FRAMEWORKS   | This will provide environment for building web based applications                             |  |  |  |

The catalog of frameworks listed above form a pattern language for building frameworks. Some of the frameworks are more general in the sense that they are applicable in other domains. But a few frameworks are specific to Graphic, CAD and GIS systems. This pattern language starts its journey from a simple function country to a complex component world.

### CONCLUSIONS

The pattern methodology is useful for documenting, communicating skill set of expert knowledge for the purpose of reuse. Development of patterns, pattern languages and frameworks are essential for every domain for enabling complex technology useful to common user and for the reuse and communication of domain expert skill set.

Using pattern at unrequited conditions create over engineering problem. Not adapting any such methods leads to under engineering problems. Extreme Programming referred as XP provides solutions for such problems.

### REFERENCES

- [1] Christopher Alexander, "An Introduction for Objectoriented Design", A lecture Note at Alexander Personal web site www.patternlanguage.com.

- [2] Pattern Languages of Program Design. Edited by James O. Coplien and Douglas C. Schmidt. Addison-Wesley, 1995.

- [3] Erich Gamma, Richard Helm, Ralph Johnson, and John Vlissides, "Design Patterns: Elements of Reusable Software Architecture", Addison-Wesley, 1995.

- [4] LNCS Transactions on Pattern Languages of Programming http://www.springer.com/computer/lncs?SGWID=0-164-2-470309-0.

- [5] Foote B, Yoder J. "Attracting Reuse". Third Conference on Pattern Languages of Programs (PLoP'96), Monticello, Illinois, September 1996

- [6] Foote B, Opdyke W. 'Life Cycle and Refactoring Patterns that Support Evolution and Reuse'. First Conference on Pattern Languages of Programs (PLoP'94). Monticello, Illinois, August, 1994.

- [7] Roberts, Don, et Ralph Johnson, Evolving Frameworks A Pattern Language for Developing Object-Oriented Frameworks, Proceedings of Pattern Languages of Programs, Allerton Park, Illinois, September 1996 (PLoP '96), Addison-Wesley, 1997.

- [8] "CHECKS Pattern Language of Information Integrity" at http://c2.com/ppr/checks.html.

- [9] Durham A, Johnson R. "A Framework for Run-time Systems and its Visual Programming Language". Proceedings of OOPSLA '96, Object-Oriented Programming Systems, Languages, and Applications. San Jose, CA. October 1996.

- [10] Dr.Hari Ramakrishna, "Design Pattern for Graphic/CAD Frameworks", Ph.D thesis submitted to Faculty of Engineering Osmania University March 2003, "Architecture of the San Francisco frameworks"—IEEE

- eeexplore.ieee.org/iel5/5288519/5387143/05387145.pdf.

- [11] Dirk Riehle and Heinz Züllighoven "Understanding and Using Patterns in Software Development" http://www.ubilab.com/publications/print\_versions/pd f/tapos-96-survey.pdf.

# Applying Principles Of Lean In Academic Environments

S.Suguna Mallika

CVR College of Engineering, Department of CSE, Ibrahimpatan, R.R.District, A.P., India Email: suguna.kishore@gmail.com

Abstract-"Lean is a philosophy that shortens the time line between the customer order and the eliminating waste." Lean is bv principally with manufacturing associated industries but can be equally applicable to both service and administration processes. Business professionals from all over the world have been studying lean principles for many years and have enjoyed tremendous bottom-line improvements by adhering to them. From the production line worker to the board of directors, everyone in an organization can benefit. Generally associated with manufacturing environments, lean is much more than a manufacturing strategy. Although its roots lie in manufacturing operations, lean is a business philosophy that can be practiced in all disciplines of an organization. This philosophy offers powerful benefits to enterprise employees, upstream suppliers, and downstream customers. The need for external collaboration is absolutely vital to a lean enterprise because all activities must be viewed holistically for true success.

Lean manufacturing is underpinned by 5 principles: Specifying what creates value from the customer's perspective, identifying all the steps along the process chain, making those processes flow, making only what is pulled by the customer, striving for perfection by continually removing wastes.

*Index Terms*-lean, lean in academic, principles of lean, TPS, and reduce waste.

### I. Introduction

Quality in a software product can be improved by process improvement, because there is a correlation between processes and outcomes. As defined by IEEE, process is "a sequence of steps performed for a given purpose." It provides project members a regular method of using the same way to do the same work. Process improvement focuses on defining continually improving process. Defects found in previous efforts are fixed in the next efforts. There are many models and techniques for process improvement, such as CMMI, ISO9000 series, SPICE, Six Sigma, etc.

Lean philosophy is to maximize customer value by eliminating waste and optimizing the existing processes in all aspects of a firm's production activities: human relations, vendor relations, technology, and the management of materials and inventory. Lean means doing more with less effort. Lean Organization understands customer value and focuses their key processes in meeting customer needs. Considers an 'end to end' value stream that delivers competitive advantage. Seeks fast flexible flow. Eliminates/prevents waste (Muda). Extends the Toyota Production System (TPS).

### II. HISTORY

Toyota first caught the world's attention in the 1980s, when it became clear that there was something special about Japanese quality and efficiency. Japanese cars were lasting longer than American cars and required much less repair. And by the 1990s it became apparent that there was something even more special about Toyota compared to other automakers in Japan (Womack, Jones, and Roos, 1991). It was not eye-popping car designs or performance though the ride was smooth and the designs often very refined. It was the way Toyota engineered and manufactured the autos that led to unbelievable consistency in the process and product. Toyota designed autos faster, with more reliability, yet at a competitive cost, even when paying the relatively high wages of Japanese workers. Equally impressive was that every time Toyota showed an apparent weakness and seemed vulnerable to the competition, Toyota miraculously fixed the problem and came back even stronger. Today Toyota is the third-largest auto manufacturer in the world, behind General Motors and Ford, with global vehicle sales of over six million per year in 170 countries [2].

### III. METHODOLOGY

Lean manufacturing is underpinned by 5 principles:

- > Specify what creates value from the customers perspective.

- ➤ Identify all the steps along the process chain.

- Make those processes flow.

- Make only what is pulled by the customer.

- Strive for perfection by continually removing wastes.

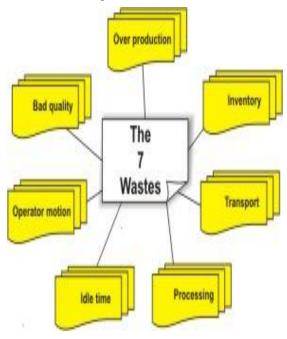

The main driver for Lean is to compress the time period being consumed by a process. In a conventional supply chain and in individual businesses, there are potentially huge amounts of different wastes, known as The 7 Wastes. The 7 wastes are depicted in the above figure as Over Production, Bad Quality, Operator motion, Transport, Inventory, Processing, Idle time et.al.[1]

### IV. TOOLS AND TECHNIQUES OF LEAN

### A. 5-S principle: The Five S's of Lean

Lean is an approach to process improvement that is well-known in manufacturing, but which can be applied to any process. These "S's" originated in Japan, and help build an environment conducive to a smooth-running process [3].

### B. Sort

Begin by eliminating unnecessary items from the work area. "Red Tagging" is an effective visual method used to identify unneeded items, which can then either be moved to a central holding area or discarded completely. This step frees up valuable floor space, removes broken or obsolete tools and fixtures, and makes it easier to focus on the job.

### C. Set in Order

The second S focuses on careful storage so the job can be carried on effectively. Some questions that must be posed are

- What do I need to do my job?

- Where should I locate this item?

- How many of this item do I need?

Other strategies for Set in Order are painting schemes that support the work, outlining work areas, shelving and cabinets for necessary items, and standard places for tools and materials needed every day. "A place for everything and everything in its place" is the essence of this 'S'.

### D. Shine

Once the first two steps are completed, and the work space is clear with needed work items in their places, it's time to thoroughly clean the work area. Because a clean and orderly area makes work easier, raises morale, and really helps staff take pride and ownership in their work and work space. A clean area also makes it easier to spot leaks, deterioration of equipment, misalignments, and broken parts that ultimately lead to equipment failure and loss of production. The impact of the clean work space will show itself in several ways on the bottom line.

### E. Standardize

This step should always involve the staff from the job or area. There are always best practices within a work function, and the first step is to find these practices and bring them to the table. The staff discusses these and come to agreement as to the best, making these the standard for all work in that particular area. But don't stop with internal best practices, encourage staff to look outside the company, even in other industries. Southwest Airlines benchmarked the Woods Brothers pit team in NASCAR to see how their fast, effective turnaround of vehicles might have application in the airlines.

### F. Sustain

This last step aims at keeping the new changes in place, and it's the toughest to implement. Because people build habits, and even when those habits are tied to poor methods of work, they're used to them and find it hard to change. Find ways to reward maintenance of these new changes, especially during the first 3 months.

### V. LEAN IN ACADEMIC ENVIRONMENTS

### A. Case Study 1

Lean can also be applied in the academic environments. Consider taking the example of academic administration. There are many challenges faced by the academic administration like "absenteeism of students". One of the tools of Lean can be used to mitigate this by the use of Visual Control Boards in the classrooms. This visual control boards should be placed for every class which is divided into parts specifying the names of the list of students who are below the threshold level of attendance and on the other side list of students who are holding the highest attendance. This certainly impacts endangered students in correcting their attendance and motivates the regularly coming students to be more regular. This visual board could be updated monthly. A sample visual board could look like as follows:

| Low Attendance(Danger)    | Green Zone (Thumbs Up)  |

|---------------------------|-------------------------|

| N.Abhishek-10B83S0213-35% | P.Sagar-10B83S0215-96%  |

| S.Suma-10B83S0238-63%     | K.Kamala-10B83S0217-93% |

|                           |                         |

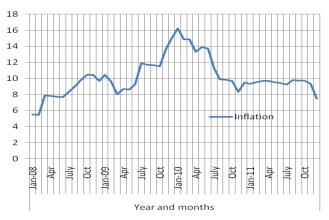

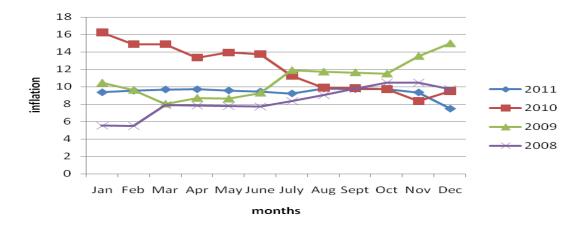

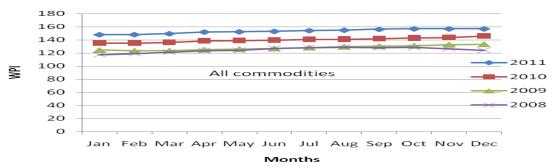

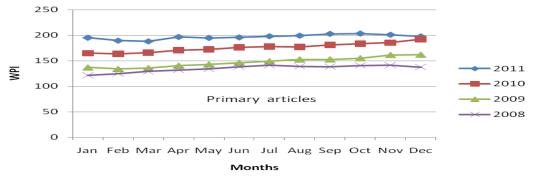

### B. Case Study 2